Indholdsfortegnelse:

- Trin 1: Materialer

- Trin 2: Black Box Diagram

- Trin 3: Tilslutning af den eksterne højttaler

- Trin 4: Strukturdiagram

- Trin 5: Finite State Machine (FSM) -diagram

Video: Konkurrencedygtigt summer -system: 5 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:26

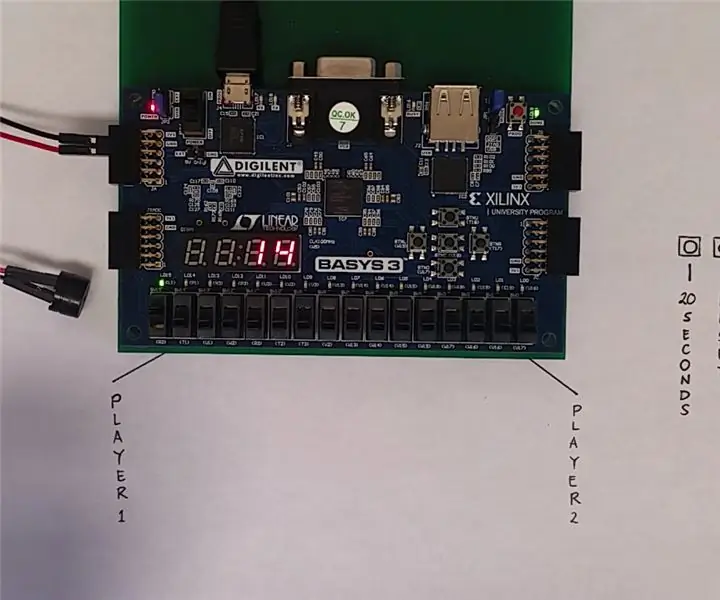

Det konkurrencedygtige summer -system, der er designet i dette projekt, fungerer på samme måde som de summer -systemer, der bruges i de regionale og nationale videnskabskonkurrencer. Dette projekt blev inspireret af mit engagement i mit gymnasiums science bowl -team i tre år. Vi har altid haft ønsket om at genskabe lock-out summer-systemet med en 5-sekunders og 20-sekunders timer.

For at give lidt baggrund om summer -systemet er science bowl -summerne programmeret til at indtaste maksimalt 8 spillere (med 8 separate summer). Når der er trykket på en summer, lyser den første persons summer for at angive, hvilken spiller der modtager spørgsmålet. Resten af spillerne bliver "låst ude", hvilket betyder, at deres summer ikke reagerer, før moderatoren nulstiller summer -systemet.

Efter at moderatoren har læst spørgsmålene, vil han trykke på en knap for at starte nedtællingstimeren, der vil blive vist på displayet med syv segmenter. Efter et "opkast" -spørgsmål kan moderatoren trykke på den højre knap for at starte nedtællingen fra 5 sekunder. I mellemtiden, efter et "bonus" -spørgsmål, kan moderatoren trykke på venstre knap for at starte nedtællingen fra 20 sekunder. Når timeren når nul, angiver en lydsummer, at afspilleren er løbet tør for tid.

For at nulstille systemet og nedtællingstimeren kan moderatoren trykke på centerknappen. For at nulstille låsemekanismen og afspillerens lysdioder skal switchene til spiller 1 og spiller 2 være lavt.

Trin 1: Materialer

Du skal bruge følgende:

- Basys3 board (eller tilsvarende FPGA board)

- Micro-B USB-kabel

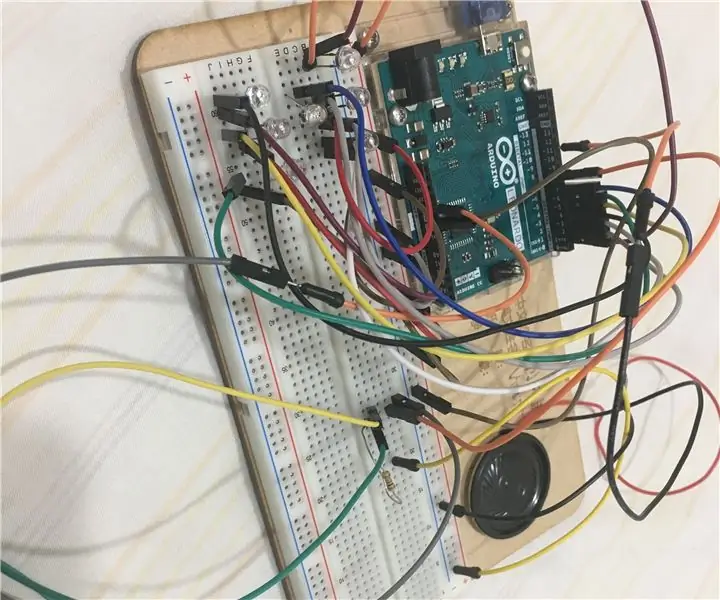

- Højttaler (jeg brugte en passiv højttaler)

- 2 ledninger

- Software til implementering på FPGA (jeg brugte Vivado)

- Konkurrencedygtig summer -fil

Trin 2: Black Box Diagram

Den sorte boksdiagram viser de input og output, der vil blive brugt i dette summer system.

INPUTS:

player1, player2 Disse indgange er forbundet til to kontakter på Basys3 -kortet. For nemheds skyld bruges kontakterne til venstre og højre til højre.

reset Den midterste knap bruges til at repræsentere reset -knappen.

count_down_20_sec Den venstre knap bruges til at repræsentere 20-sekunders timer-knappen.

count_down_5_sec Den højre knap bruges til at repræsentere 20-sekunders timer-knappen. For at sikre, at både 20-sekunders og 5-sekunders timeren starter, skal du holde knappen nede, indtil displayet i syv segmenter viser timeren.

CLK FPGA -kortet genererer et ur, der kører med en frekvens på 10 ns.

UDGANG:

højttaler Højttalerudgangen er tilsluttet en ekstern summer eller højttaler. Du bliver nødt til at tilslutte højttaleren til Basys3 -kortets JA pmod -porte. Dette trin vil blive beskrevet nedenfor.

speaker_LED Denne udgang er tilsluttet en LED på midten af kortet, og angiver bare, når højttalerudgangen på FPGA er høj. Du kan bruge dette til at teste din eksterne højttaler. Bemærk, at nogle af pmod -portene muligvis ikke fungerer godt, så du kan prøve forskellige og bruge LED'en til at kontrollere, om højttaleren skal være tændt.

SEGMENTER Denne output er forbundet til de otte individuelle segmenter på syv-segmentets display, inklusive decimalpunktet.

DISP_EN Denne udgang er forbundet til de fire anoder på syv-segment displayet.

player_LED Denne udgang er et 2-bundt signal, der er forbundet til lysdioderne over afspiller1 og afspiller2 switches. Den første spiller, der vender den tilhørende switch, vises med LED'en. Bemærk, at begge lysdioder ikke kan være tændt samtidigt.

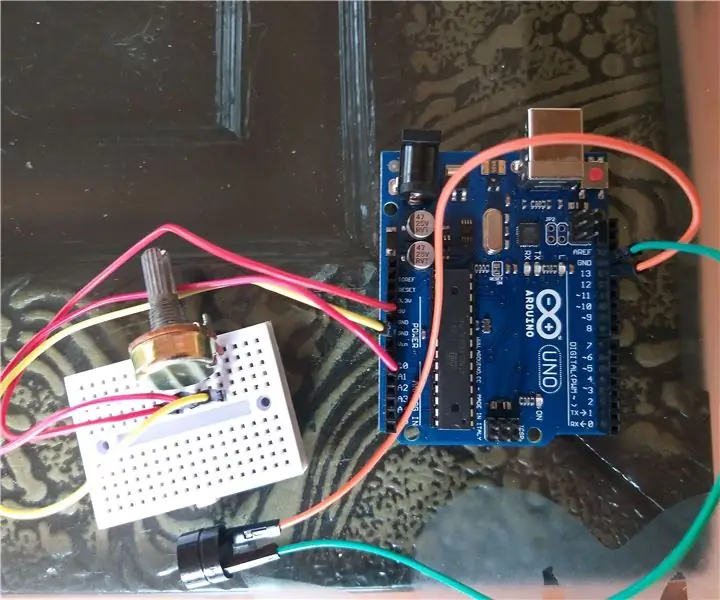

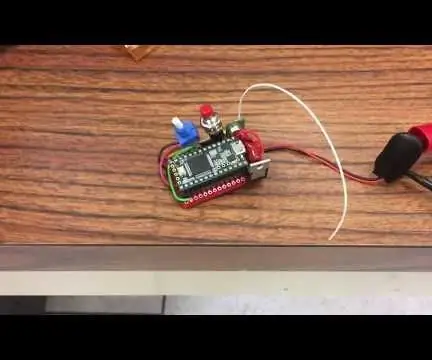

Trin 3: Tilslutning af den eksterne højttaler

For at slutte den eksterne højttaler til Basys3 -kortet skal du tage dine to ledninger og vedhæfte dem som angivet på billedet ovenfor. Den hvide linje forbinder højttalerens negative terminal med jordporten på kortet. Den røde linje forbinder højttalerens positive terminal med JA10 pmod -porten på kortet.

Begrænsningsfilen er designet, så enhver port fra JA1 til JA10 skal fungere. Nogle stifter på tavlen reagerer dog ikke, så hvis JA10 ikke fungerer, kan du prøve de andre porte.

Trin 4: Strukturdiagram

Billedet ovenfor viser strukturdiagrammet over det konkurrencedygtige summer -system, herunder alle de komponenter, der udgør hovedmodulet. Deres beskrivelser er som følger:

player_lockout_LED1 Spillerens lockout-LED-komponent er en endelig maskine, der bruger en-hot-kodning. Den har fire indgange: player1, player2, reset og CLK. Den indeholder en 2-bit bundle output player_LED. Indgange og udgange af player_lockout_LED1-komponenten er alle direkte forbundet med de identisk navngivne indgange og udgange af hovedmodulet.

buzzer_tone1 Buzzer -komponenten er baseret på denne kode, der er lagt ud på et forum

stackoverflow.com/questions/22767256/vhdl-… Det blev dog ændret til at udsende en kontinuerlig lyd med en frekvens på 440 Hz (en note). Aktiveringsindgangen er forbundet til et buzzer_enable -signal, som er et output fra down_counter_FSM1 -komponenten.

clk_div1 Urdelerkomponenten er en modificeret version af professor Bryan Mealys urdeler, der findes på PolyLearn. Det bremser uret, så outputperioden er 1 sekund.

down_counter_FSM1 Nedtælleren er en FSM designet til at tælle ned til nul. De to mulige starttider er 20 eller 5, som vælges af brugerinput. Den sender '1', når timeren har nået nul for at indikere, at tiden er løbet ud. Denne udgang fungerer som en aktivering for summertonekomponenten. Tælleren udsender også et 8-bit bundtsignal, der sender en 8-bit BCD, der sendes til segmentdekoderen. En anden output er counter_on, som også er forbundet til den gyldige input på segmentdekoderen.

sseg_dec1 Den syv-segment dekoder-komponent findes på PolyLearn og er skrevet af professor Bryan Mealy. Den bruger en BCD-input fra down_counter_FSM1 og udsender decimalækvivalenten på displayet med syv segmenter. Når tælleren er tændt, er det gyldige input højt. Dette gør det muligt for dekoderen at vise decimaltallet på syv segmenters display. Når tælleren er slukket, er den gyldige input lav. Displayet med syv segmenter viser derefter kun fire streger.

Trin 5: Finite State Machine (FSM) -diagram

Følsomhedslisten for den endelige tilstandsmaskine inkluderer player1, player2, reset og uret. FSM-udgangen er en 2-bit bundt player_LED forbundet til to lysdioder på Basys3-kortet. Den endelige tilstandsmaskine viser følgende tre tilstande:

ST0 er starttilstanden. I denne tilstand er de to lysdioder slukket. FSM vil forblive i denne tilstand, hvis både player1 og player2 er lave. En asynkron nulstilling sætter også tilstanden til ST0. Når afspiller1 -kontakten er sat til høj, vil den næste tilstand være ST1. Hvis afspiller2 -kontakten er sat til høj, er den næste tilstand ST2.

ST1 er den tilstand, som afspiller1 LED er tændt for. FSM vil forblive i denne tilstand for alle input. Det betyder, at selv når afspiller2 -kontakten er sat til høj umiddelbart efter, at afspiller1 -kontakten er høj, forbliver den i ST1. Kun den asynkrone nulstilling kan indstille den næste tilstand til ST0.

ST2 er den tilstand, som player2 LED er tændt for. Ligesom ST !, vil FSM forblive i denne tilstand for alle input, selv når afspiller1 -kontakten er sat til høj umiddelbart efter, at afspiller2 -kontakten er høj. Igen er det kun den asynkrone nulstilling, der kan indstille den næste tilstand til ST0.

Anbefalede:

Summer Fan Cooling Baseball Cap: 6 trin

Summer Fan Cooling Baseball Cap: En dag da jeg rodede i min garderobe, så jeg en gammel rød baseball cap, som jeg har købt sidste år. Pludselig og en idé dukkede op i mit sind, kunne jeg ændre denne gamle kasket til et køligt produkt, der hedder fan hat, et helt specielt innovationsprodukt

Super Mario ved hjælp af summer: 3 trin

Super Mario Using Buzzer: Lytte til musik slapper af vores sind og sjæl. Lad os tilføje noget musik til dine arduino -projekter ved hjælp af en enkelt komponent, buzzer. Jeg fandt dette fantastiske projekt ved hjælp af Buzzer, der spiller super marios temasang skrevet af Dipto Pratyaksa på instruktører. Desuden

Fjernstyret summer til fortabt og fundet: 4 trin

Fjernstyret summer til tabt og fundet: Dette todelt kredsløb består af en summer og en controller. Sæt summeren på et emne, du ofte kan miste, og brug knappen og lydstyrkeknappen på controlleren til at aktivere summeren, når elementet går tabt. Summer og kontrolenhed

LED -terninger med summer: 6 trin

LED-terninger med summer: Denne instruktive lærer dig, hvordan du laver en LED-terning med summer, når der trykkes på knappen. Original kilde: https://www.instructables.com/id/Easy-Arduino-LED-Dice

Sådan bruges summer HW-508 med SkiiiD: 8 trin

Sådan bruges buzzer HW-508 med SkiiiD: Dette projekt er en instruktion om, hvordan du bruger Buzzer HW-508 (gælder for KY-006) med Arduino via skiiiD Inden start er nedenfor en grundlæggende vejledning til, hvordan du bruger skiiiD https: //www.instructables.com/id/Getting-Started-W