Indholdsfortegnelse:

- Trin 1: System Black Box

- Trin 2: Komponenter

- Trin 3: D flip-flops

- Trin 4: Betingelser

- Trin 5: Begrænsninger

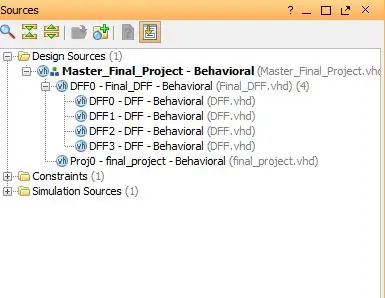

- Trin 6: Hovedkildefil

- Trin 7: Montering

- Trin 8: Indlæser programmet

Video: Energieffektiv bevægelsesaktiveret gadebelysning: 8 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:27

Vores mål med dette projekt var at skabe noget, der ville spare samfund for energi og økonomiske ressourcer. Bevægelsesaktiverede gadelamper ville gøre begge disse ting. Overalt i landet spildes energi på gadelamper, der tænder gader, der er tomme. Vores gadebelysningssystem sikrer, at lys kun er tændt, når det er nødvendigt, hvilket sparer samfund for utallige dollars. Ved hjælp af bevægelsessensorer tænder systemet kun lys, når biler er til stede. Også for fodgængernes sikkerhed implementerede vi en overstyringsknap, der tænder alle lys på gaden. De følgende trin vil guide dig gennem, hvordan vi designede og byggede vores nedskalerede model af projektet ved hjælp af Vivado og et Basys 3 -bord.

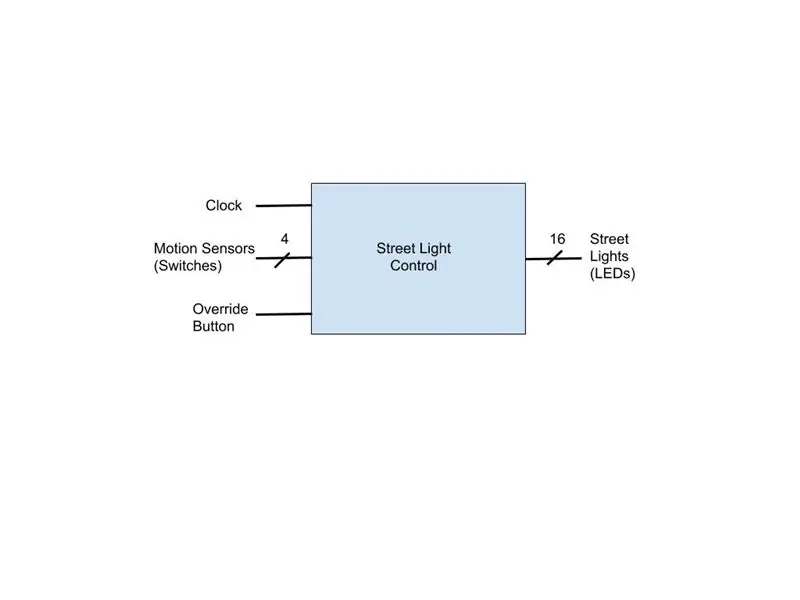

Trin 1: System Black Box

Vi startede dette projekt med at tegne et simpelt sortboksdiagram. Et sort boksdiagram viser simpelthen de input og output, som vores system kræver for at fuldføre alle nødvendige processer. Vi forsøgte at holde vores design så enkelt og grundlæggende som muligt. Vores tre systemindgange inkluderede en bus med bevægelsessensorer (4 til vores nedskalerede model), en knap til overstyring af fodgængere og et urindgang. På den anden side er vores eneste output en bus med LED -lys, der repræsenterer vores gadelamper. Til denne model brugte vi et scenario med 16 gadelamper, simpelthen fordi det er det maksimale antal indbyggede LED -udgange på Basys 3 -kortet. Endelig kunne vi ved hjælp af dette diagram oprette vores Vivado -projekt, kilde- og begrænsningsfiler med passende input og output.

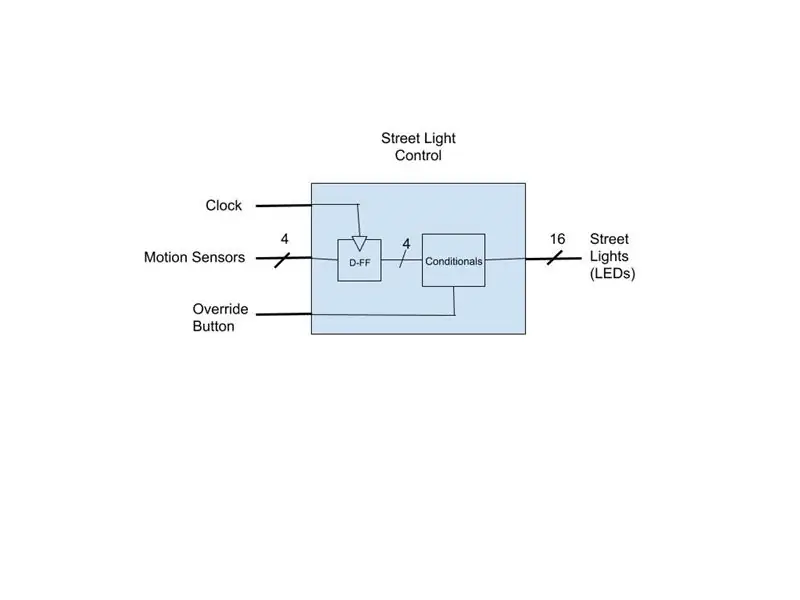

Trin 2: Komponenter

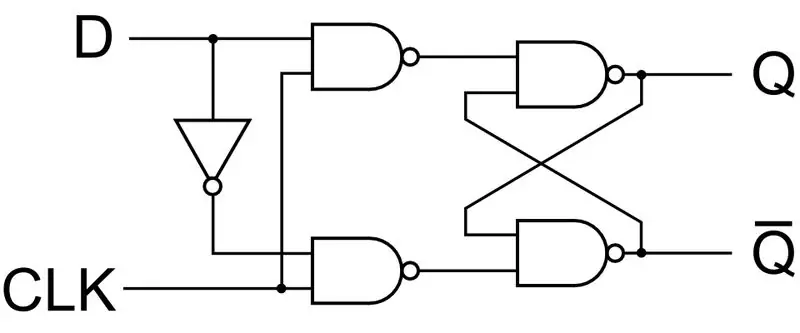

I dette trin dykker vi dybere og undersøger komponenterne i vores black box -diagram. Vores første komponent er en VHDL-kildefil, der indeholder D-flip-flops. D flip-flops tager simpelthen det signal, der sendes til dem fra sensorerne på urets stigende kant, og låser disse data ind indtil den næste stigende kant. Dette forhindrer vores følsomme bevægelsessensorer i at forårsage, at output -LED'erne "flimrer". Vi sætter også en enkelt D flip-flop på knappens indgangssignal for at holde lysdioderne tændt i cirka 5-7 sekunder efter at knappen er trykket. Vi kørte også dette gennem en urdeler.

enhed clk_div2 er Port (clk: in std_logic; sclk: out std_logic); slut clk_div2;

arkitektur my_clk_div af clk_div2 er

konstant max_count: heltal: = (300000000); signal tmp_clk: std_logic: = '0'; begynde my_div: proces (clk, tmp_clk) variabel div_cnt: heltal: = 0; begynde hvis (stigende_kant (clk)) derefter hvis (div_cnt = MAX_COUNT) derefter tmp_clk <= ikke tmp_clk; div_cnt: = 0; ellers div_cnt: = div_cnt + 1; Afslut Hvis; Afslut Hvis; sclk <= tmp_clk; afslutte processen my_div; afslut my_clk_div;

Vores sidste komponent i dette diagram er en adfærdsmæssig VHDL -kildefil, der indeholder betingelser for output, baseret på konfigurationen af indgangssignaler.

Trin 3: D flip-flops

De fire flip-flops, der er knyttet til indgangssignalerne, er afgørende for vores systems funktionalitet. Som sagt tidligere, med følsomme bevægelsessensorer og en overstyringsknap, bruger flip-flopsne låse til kun at udsende vores indgangssignal på den stigende kant af uret. Denne sekventielle logik betyder, at vores gadebelysning kan forblive tændt i en bestemt periode efter at være blevet udløst af en hurtig bevægelse. Kodningen til en D-Flip Flop er ret enkel:

beginprocess (CLK) begynder hvis rising_edge (CLK) derefter Q <= D; Afslut Hvis; afslutte processen;

Det hele kan samles til en enkelt if -sætning. Når vi havde dette stykke, oprettede vi en strukturel VHDL-kildefil, der indeholder alle fire af vores nødvendige flip-flops:

begynde DFF0: DFF -portkort (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF -portkort (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF -portkort (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF -portkort (CLK => CLK, D => D (3), Q => Q (3));

ende Adfærdsmæssig;

Dette hjælper med at holde vores hovedstrukturfil, hvor vi samler alle systemkomponenter meget mere rene og organiserede.

Trin 4: Betingelser

For at holde vores kode kompakt og effektiv skrev vi alle vores betingelser i en enkelt sagserklæring. For vores nedskalerede model havde vi 16 mulige LED -udgangskonfigurationer, da hver bevægelsessensor er ansvarlig for en gruppe på 4 LED'er.:

tilfælde NMS er når "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; slut sag;

Trin 5: Begrænsninger

For korrekt at angive dine input og output ved hjælp af Vivado, skal du implementere en begrænsningsfil, der angiver alle porte, knapper, LED'er og ure, der bruges.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports_ LED] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_ LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11] }33_] [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Trin 6: Hovedkildefil

I denne hovedfil samler vi alle tidligere nævnte komponentkildefiler. Denne fil fungerer som strukturel kode, der samler de forskellige komponenter.

enhed Master_Final_Project er Port (BTN: i STD_LOGIC; CLK: i STD_LOGIC; MS: i STD_LOGIC_VECTOR (3 ned til 0); LED: ud STD_LOGIC_VECTOR (15 ned til 0)); afslut Master_Final_Project;

arkitektur Adfærdsmæssig for Master_Final_Project er

komponent final_project er Port (--CLK: i STD_LOGIC; NMS: i STD_LOGIC_VECTOR (3 ned til 0); BTN: i STD_LOGIC; --sw: i STD_LOGIC_Vector (1 ned til 0); LED: ude STD_LOGIC_VECTOR (15 ned til 0)); slutkomponent;

komponent Final_DFF er

Port (CLK: i STD_LOGIC; D: i STD_LOGIC_Vector (3 ned til 0); Q: ud STD_LOGIC_Vector (3 ned til 0)); slutkomponent;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

begynde

DFF0: Final_DFF portkort (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: final_project port map (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); ende Adfærdsmæssig;

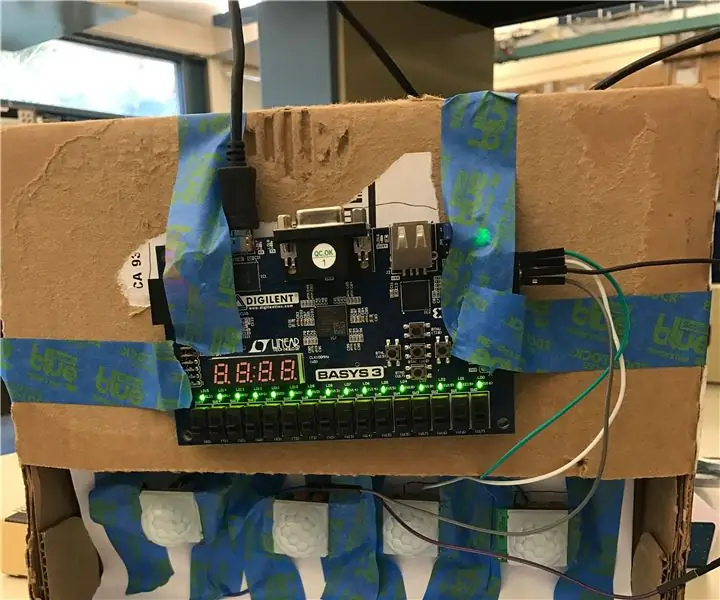

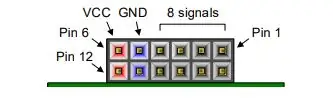

Trin 7: Montering

Hardware -samlingen til dette projekt er minimal. De eneste nødvendige stykker er som følger:

1. Basys 3 board (1)

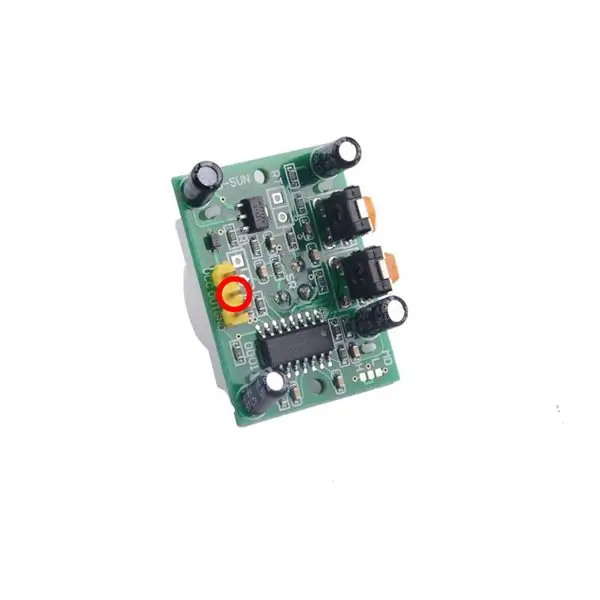

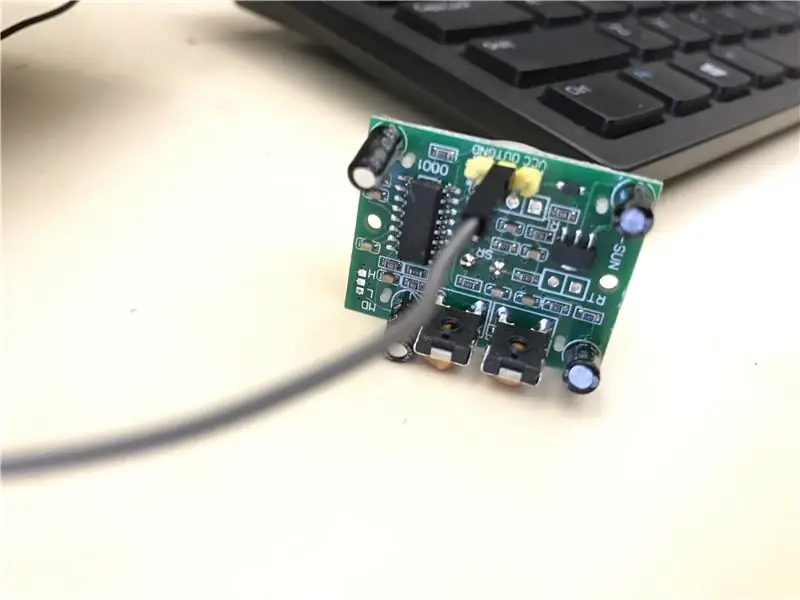

2. Billige bevægelsessensorer, der kan findes på amazon her. (4)

3. Mand-til-hun-kundeemner (4)

Montage:

1. Tilslut 4 hanledninger til PMod header JB-porte 1-4 (se figur).

2. Tilslut hunender til hver bevægelsessensors udgangsstift.

Trin 8: Indlæser programmet

Nu er vi klar til at indlæse VHDL -master -kildefilen til Basys 3 -kortet. Sørg for at køre syntese, implementering og generere bitstreamkontrol for eventuelle fejl. Hvis alle kører med succes, skal du åbne hardwarehåndteringen og programmere Basys 3 -enheden. Dit projekt er nu færdigt!

Anbefalede:

Bevægelsesaktiveret lampekontakt: 3 trin

Bevægelsesaktiveret lampekontakt: Når vi forlader vores skrivebord eller værelse, glemmer vi det meste af tiden at slukke lyset der. Dette medfører tab af elektricitet og stigning i din elregning. Men hvad nu, hvis lysene slukker automatisk, når du forlader rummet. Ja i

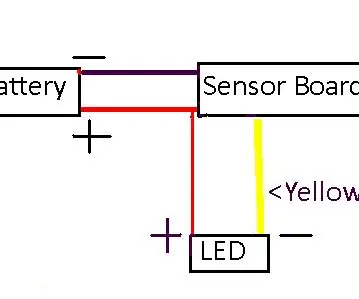

Batteridrevet bevægelsesaktiveret LED-lampe: 4 trin

Batteridrevet bevægelsesaktiveret LED-lampe: Hvis du gerne vil sætte et lys et sted, der ikke egner sig til at blive tilsluttet, kan det være lige hvad du har brug for

Sådan laver du automatisk gadebelysning ved hjælp af LM555 IC: 8 trin

Sådan laver du automatisk gadebelysning ved hjælp af LM555 IC: Hej ven, I dag skal jeg lave et kredsløb af automatisk gadebelysning ved hjælp af LM555 IC.Dette kredsløb fungerer sådan Når lyset falder på LDR (In Day), så lyser LED ikke og når lys ikke vil være på LDR, lyser LED automatisk

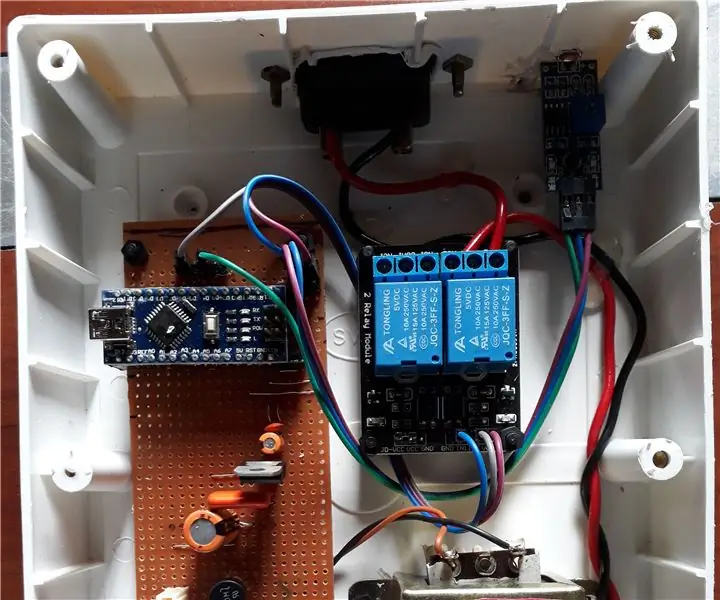

Bevægelsesaktiveret lyskontakt med lyssensor: 5 trin

Bevægelsesaktiveret lysafbryder med lyssensor: Bevægelsesaktiveret lysafbryder har mange applikationer både hjemme og på kontoret. Dette har imidlertid en ekstra fordel ved at inkorporere en lyssensor, så dette lys kun kan udløses om natten

Bevægelsesaktiveret Redstone: 7 trin (med billeder)

Bevægelse Aktiveret Redstone: Hej der! Dette projekt er en bevægelsesaktiveret redstone lampe. Det fungerer ved at bruge en smuldret mikrokontroller og en ultralydsafstandssensor, der er forbundet til et relæ. Dette projekt deltager i minecraft -konkurrencen og eventuelle stemmer, favoritter eller co