Indholdsfortegnelse:

- Trin 1: Specifikationer

- Trin 2: RTL -visning af hele systemet

- Trin 3: Testresultater

- Trin 4: Vedhæftede filer

Video: Design af en simpel 4-vejs sæt associeret cache-controller i VHDL: 4 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:27

I min tidligere instruerbare så vi, hvordan vi designede en simpel direkte kortlagt cache -controller. Denne gang går vi et skridt foran. Vi vil designe en simpel associeret cache-controller med fire veje. Fordel? Mindre fejlrate, men på bekostning af ydeevne. Ligesom min tidligere blog, ville vi designe og efterligne en hel processor, hovedhukommelse og cachemiljø for at teste vores cachecontroller. Jeg håber, at I finder dette som en nyttig reference til at forstå begreberne og designe jeres egne cachecontrollere i fremtiden. Da modellen til processor (testbænk) og hovedhukommelsessystemet er nøjagtig det samme som min tidligere blog, vil jeg ikke forklare dem igen. Se venligst den tidligere instruerbare for detaljer om det.

Trin 1: Specifikationer

Hurtigt kig gennem specifikationerne for Cache Controller præsenteret her:

- Four-way Set Associative Cache Controller (gå til dette link, hvis du leder efter Direct Mapped Cache Controller).

- Enkeltbanket, blokerende cache.

- Gennemførelsespolitik for skrivehits.

- Skriv-rundt-politik om skrivefejl.

- Tree Pseudo-LRU (pLRU) udskiftningspolitik.

- Tag Array i controlleren.

- Konfigurerbare parametre.

Standardspecifikationer for cachehukommelse og hovedhukommelse er de samme som fra min tidligere instruerbare. Henvis venligst til dem.

Trin 2: RTL -visning af hele systemet

Komplet RTL -repræsentation af topmodulet er vist i figuren (undtagen processoren). Standardspecifikationer for busserne er:

- Alle databusser er 32-bit busser.

- Adressebus = 32-bit bus (men kun 10 bit kan adresseres her af hukommelsen).

- Datablok = 128 bits (Wide Bandwidth Bus for Read).

- Alle komponenter drives af det samme ur.

Trin 3: Testresultater

Topmodulet blev testet ved hjælp af en testbænk, der simpelthen modellerer en ikke-pipelineret processor, ligesom vi gjorde i den sidste instruerbare. Testbænken genererer ofte læse/skrive dataanmodninger til hukommelsen. Dette håner typiske "Load" og "Store" instruktioner, der er almindelige i alle programmer, der udføres af en processor.

Testresultaterne bekræftede succesfuldt cachecontrollerens funktionalitet. Følgende er teststatistikken observeret:

- Alle Læs/skriv miss- og hit -signaler blev genereret korrekt.

- Alle læse-/skrivedataoperationer var vellykkede på alle fire måder.

- pLRU -algoritmen er med succes verificeret til udskiftning af cachelinjer.

- Der blev ikke fundet problemer med datainkoherens/inkonsistens.

- Designet blev med succes verificeret for en maks. Ur Driftsfrekvens = 100 MHz i Xilinx Virtex-4 ML-403 Board (hele systemet), 110 MHz til Cache Controller alene.

- Blok -RAM'er blev udledt for hovedhukommelsen. Alle andre arrays blev implementeret på LUT'er.

Trin 4: Vedhæftede filer

Følgende filer er vedhæftet her med denne blog:

- . VHD -filer fra Cache Controller, Cache Data Array, Main Memory System.

- Testbænk.

- Dokumentation om Cache Controller.

Bemærkninger:

- Gennemgå dokumentationen for fuld forståelse af specifikationerne for cache -controlleren, der præsenteres her.

- Eventuelle ændringer i koden afhænger af andre moduler. Så ændringerne bør gøres omhyggeligt.

- Vær opmærksom på alle de kommentarer og overskrifter, jeg har givet.

- Hvis der af en eller anden grund ikke udledes Block RAM'er for hovedhukommelsen, reducer hukommelsens størrelse efterfulgt af ændringer i adressebussbredder på tværs af filerne og så videre. Så den samme hukommelse kan implementeres enten på LUT'er eller distribueret RAM. Dette vil spare routing tid og ressourcer. Eller gå til den specifikke FPGA -dokumentation, og find den kompatible kode til Block RAM, og rediger koden i overensstemmelse hermed, og brug de samme adressebusbreddespecifikationer. Samme teknik for Altera FPGA'er.

Anbefalede:

Fuldt IR -tilpasseligt elektronisk sæt med otte terninger: 14 trin (med billeder)

Fuldt IR -tilpasseligt elektronisk sæt med otte terninger: I samarbejde med J. Arturo Espejel Báez Nu kan du have op til 8 terninger fra 2 til 999 ansigter i en 42 mm diameter og 16 mm høj etui! Spil dine yndlingsbrætspil med dette konfigurerbare elektroniske sæt terninger i lommestørrelse! Dette projekt består af

Sæt Chromcast på pause med en fjernbetjening: 5 trin

Sæt Chromcast på pause med en fjernbetjening: Jeg har en Logitech Harmony -fjernbetjening og kører hjemmeassistent på en hindbærpi. Jeg ønskede at kunne sætte Chromecast på pause fra min fjernbetjening, men jeg har et gammelt tv, der ikke understøtter dette via hdmi. Min idé var derefter at bruge en NodeMcu til at fange IR -signalet og

Vend en ATGAMES bærbar Sega Genesis til et trådløst sæt højttalere .: 13 trin (med billeder)

Gør et ATGAMES bærbart Sega Genesis til et trådløst sæt højttalere.: Hvis du har læst min første instruktion om, hvordan du ændrer et nyt bedre batteri til ATGAMES bærbare Sega Genesis, vil du måske undre dig over: Sp: Hvad ville jeg gøre med alle den nyfundne magt? A: Rediger ATGAMES Portable Sega Genesis til en wirele

Trin-for-trin uddannelse i robotik med et sæt: 6 trin

Trin-for-trin uddannelse i robotteknologi med et kit: Efter ganske få måneder med at bygge min egen robot (se alle disse), og efter at jeg to gange havde dele mislykkedes, besluttede jeg at tage et skridt tilbage og tænke min strategi og retning. De flere måneders erfaring var til tider meget givende, og

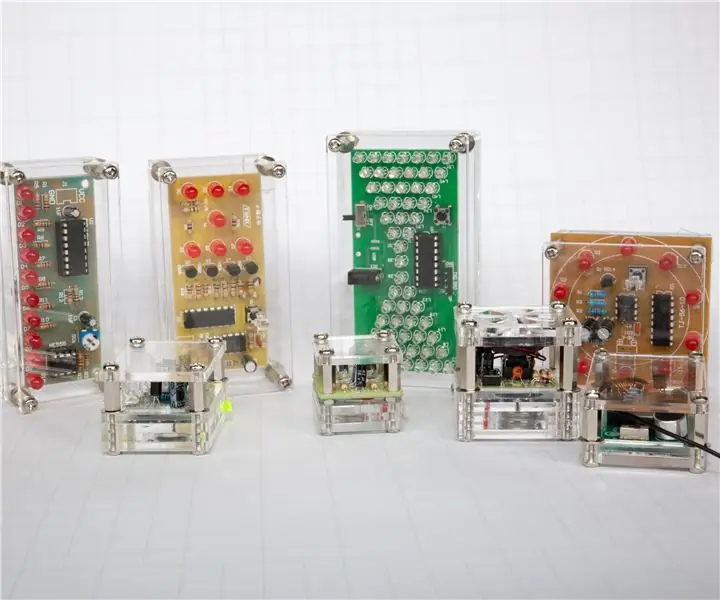

Batterikasser til elektroniske sæt: 11 trin (med billeder)

Batterikasser til elektroniske kits .: Hvis du har bygget et af de billige elektroniske kits, der var beskrevet i min tidligere instruerbare, vil du sandsynligvis lægge en slags sag i. At have dit projekt i en flot sag vil virkelig få dit projekt til at se godt ud og vil imponere dine venner