Indholdsfortegnelse:

- Trin 1: Materialer

- Trin 2: Indstilling af input og output

- Trin 3: Fremstilling af ure

- Trin 4: Tæller til ti

- Trin 5: Visning af tal

- Trin 6: Sådan vises stopuret

- Trin 7: Saml det hele

- Trin 8: Begrænsninger

- Trin 9: Test

Video: Grundlæggende stopur ved hjælp af VHDL og Basys3 Board: 9 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:28

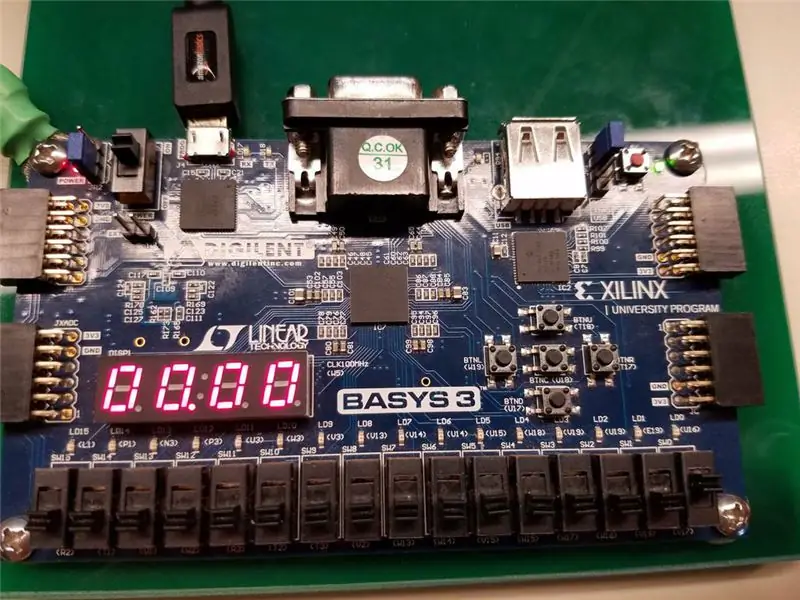

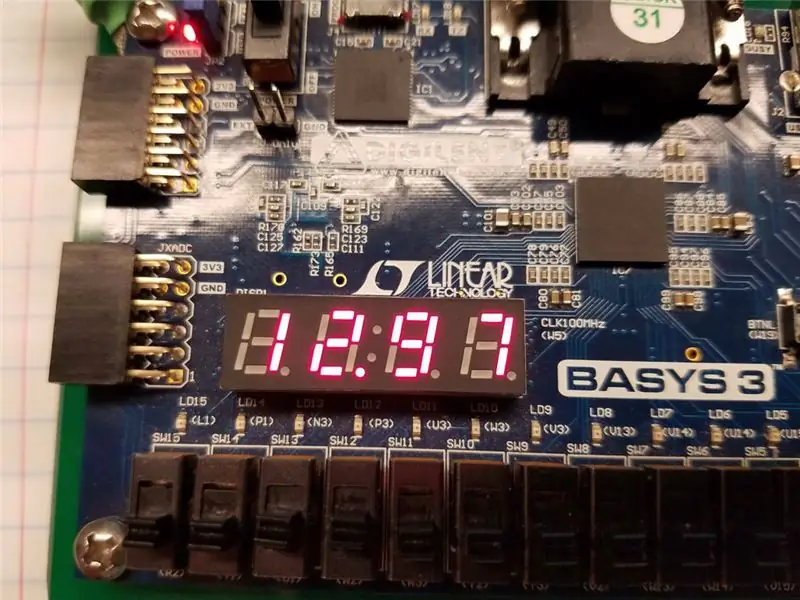

Velkommen til instruktionsbogen om, hvordan man bygger et stopur ved hjælp af grundlæggende VHDL og Basys 3 -kort. Vi glæder os til at dele vores projekt med dig! Dette var et afsluttende projekt for kursus CPE 133 (Digital Design) på Cal Poly, SLO i efteråret 2016. Projektet, vi byggede, er et simpelt stopur, der starter, nulstiller og sætter tiden på pause. Det tager tre trykknapper på Basys3-kortet som input, og tiden vises på tavlens firecifrede syv-segment display. Den forløbne tid vises i formatet sekunder: centisekunder. Det bruger tavlens systemur som input til at holde styr på den forløbne tid og sender tiden ud til de fire cifre i syvsegmentets display.

Trin 1: Materialer

De materialer, du skal bruge til dette projekt:

- 1 computer med Vivado Design Suite WebPack installeret fra Xilinx (foretrækker version 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA board

- 1 USB -portkabel

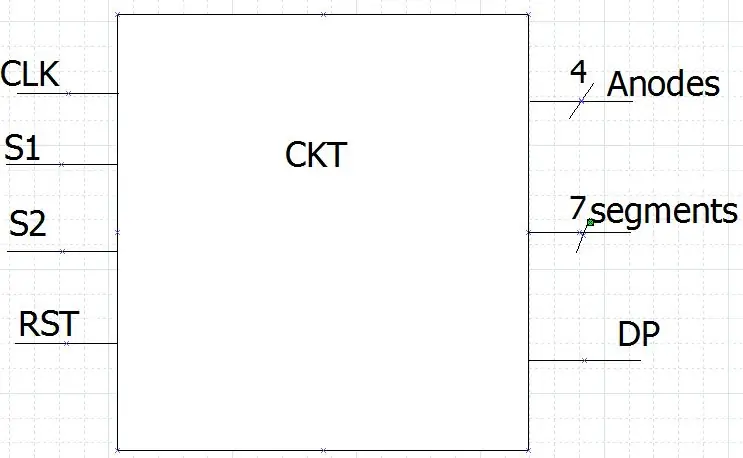

Trin 2: Indstilling af input og output

Ovenstående figur viser et blokdiagram på øverste niveau af stopurmodulet. Stopuret indtaster input "CLK" (ur), "S1" (startknap), "S2" (pause-knap) og "RST" (reset) og har en 4-bit output "Anodes", en 7-bit output "segment" og et single-bit output "DP" (decimalpunkt). Når input "S1" er høj, begynder stopuret at tælle tid. Når "S2" er lav, stopper uret tiden. Når "RST" er høj, stopper stopuret og nulstiller tiden. Der er fire delmoduler inden for kredsløbet: urdeleren, ciffer-tælleren, syv-segment display driveren og syv-segment display encoder. Stopurets hovedmodul forbinder alle delmodulerne sammen og til input og output.

Trin 3: Fremstilling af ure

Urdelermodulet optager et systemur og bruger en divisorindgang til at oprette et ur med enhver hastighed, der ikke er større end systemurets. Stopuret bruger to forskellige urmoduler, et som skaber et 500 Hz ur og et andet som skaber et 100 Hz ur. Skematikken for urdeleren er vist i figuren ovenfor. Urdeleren optager en single-bit input "CLK", og en 32-bit input "Divisor" og single-bit output "CLKOUT". "CLK" er systemuret og "CLKOUT" er det resulterende ur. Modulet indeholder også en NOT -port, som skifter signal "CLKTOG", når tællingen når værdien af divisoren.

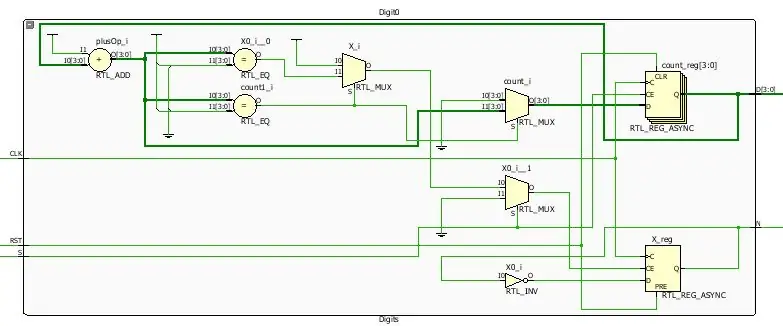

Trin 4: Tæller til ti

Cifretælleren tæller hvert ciffer fra 0 til 10 og opretter et andet ur til det næste ciffer, der skal fungere ud af det, oscillerer, når tællingen når 10. Modulet optager 3 single-bit input "S", "RST" og "CLK "og resulterer i et single-bit output" N "og et 4-bit output" D ". Input "S" er aktiveringen i input. Uret tændes, når "S" er højt og slukket, når "S" er lavt. "RST" er nulstillingsindgangen, så uret nulstilles, når "RST" er højt. "CLK" er urindgangen til ciffertælleren. "N" er urudgangen, der bliver inputuret for det næste ciffer. Output "D" viser den binære værdi af det ciffer, tælleren er på.

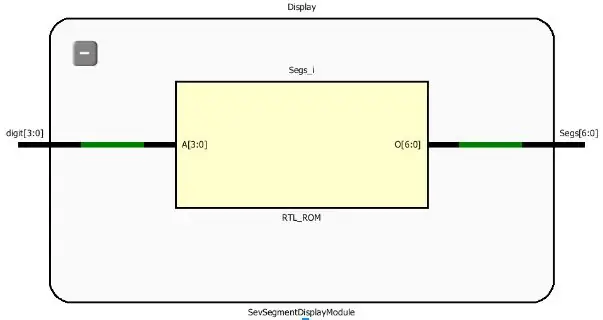

Trin 5: Visning af tal

Syv-segment displaykoderen vil kode det binære tal, der modtages fra syv-segment display-drivermodulet og gøre det til en strøm af bits, der vil blive fortolket som '1' eller '0' værdier for hvert segment af displayet. Det binære tal modtages af modulet som 4-bit input "ciffer" og resulterer i 7-bit output "segmenter". Modulet består af en enkelt sagsprocessblok, der tildeler en specifik 7-bit-strøm til hver mulig inputværdi fra 0 til 9. Hver bit i syv-bitstrømmene repræsenterer et af de syv segmenter af cifrene på displayet. Rækkefølgen af segmenterne i strømmen er "abcdefg" med '0'er, der repræsenterer de segmenter, der lyser for det givne tal.

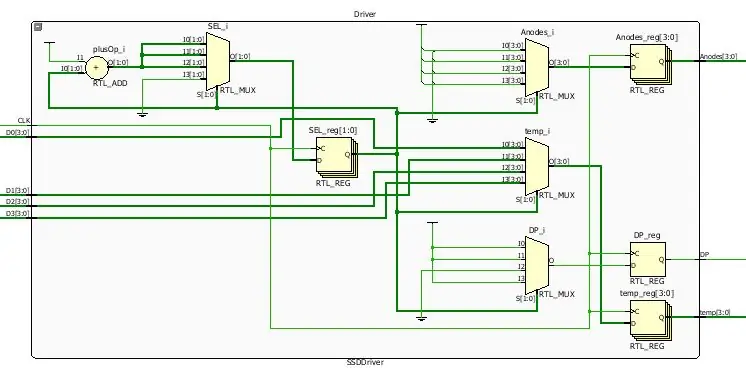

Trin 6: Sådan vises stopuret

I syv-segment display driver-modulet er der fire 4-bit input "D0", "D1", "D2" og "D3", der hver repræsenterer de fire cifre, der skal vises. Input "CLK" er systemets urindgang. Enkeltbit-output "DP" repræsenterer decimaltegnet på syv-segmentets display. 4-bit udgangen "Anoder" bestemmer, hvilket ciffer på syv-segment displayet, og 4-bit output "temp" afhænger af tilstanden af 2-bit kontrol input "SEL". Modulet anvender 4 multiplexere til styreenheden "SEL" og de tre udgange; "Anoder", "temp" og "DP".

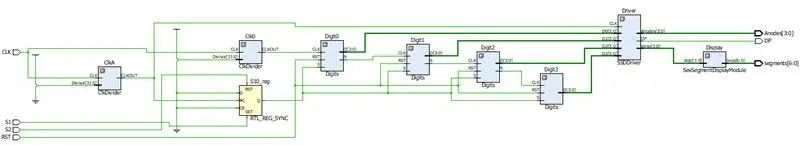

Trin 7: Saml det hele

En 'hvis' procesblok, der kører af 500Hz -uret, bruges til at oprette start- og pause -knapperne. Link derefter alle submodulerne sammen i stopurets hovedmodul ved at deklarere komponenterne i hver enkelt submodul og bruge forskellige signaler. Cifferundermodulerne optager urudgangen fra den foregående cifret submodul, hvor den første tager 100Hz -uret. "D" -udgange fra cifferundermodulerne bliver derefter til "D" -indgange i det syv segment display -drivermodul. Og endelig bliver "temp" -output fra syv segment display driver modul til "temp" input for det syv segment encoder modul.

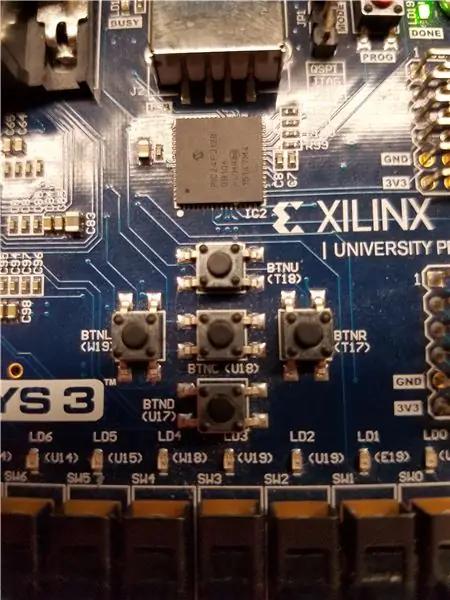

Trin 8: Begrænsninger

Brug 3 trykknapper (W19, T17 og U18) til input "RST", "S1" og "S2". W19 er nulstillingsknappen, T17 er startknappen (S1), og U18 er pauseknappen (S2). En begrænsning for urindgangsindgangen er også påkrævet ved brug af port W5. Husk også at tilføje denne linje til urbegrænsningen:

create_clock -add -name sys_clk_pin -periode 10.00 -bølgeform {0 5} [get_ports {CLK}]

Link også anoderne og segmenterne til tavlen, så stopuret vises på syvsegments displayet som det ses i begrænsningsfilen.

Trin 9: Test

Sørg for, at din enhed fungerer ved at spille med de tre knapper: trykke på og holde dem i enhver mulig rækkefølge for at finde mulige problemer med din kode.

Anbefalede:

Sådan laver du et grundlæggende websted ved hjælp af Notesblok: 4 trin

Sådan laver du et grundlæggende websted ved hjælp af notesblok: Er der nogen, der har spekuleret i "hvordan laver jeg et websted ud af et grundlæggende skriveprogram?" Nå, selvfølgelig, ikke specifikt … Anyway, her viser jeg dig, hvordan du laver en BASIC websted, der kun bruger notesblok

NAIN 1.0 - den grundlæggende humanoide robot ved hjælp af Arduino: 6 trin

NAIN 1.0 - den grundlæggende Humanoid -robot, der bruger Arduino: Nain 1.0 vil have dybest set 5 aftagelige moduler- 1) Arm - som kan styres via servoer. 2) Hjul - som kan styres med jævnstrømsmotorer. 3) Ben - Nain vil være i stand til at skifte mellem hjul eller ben for bevægelse. 4) Hoved og

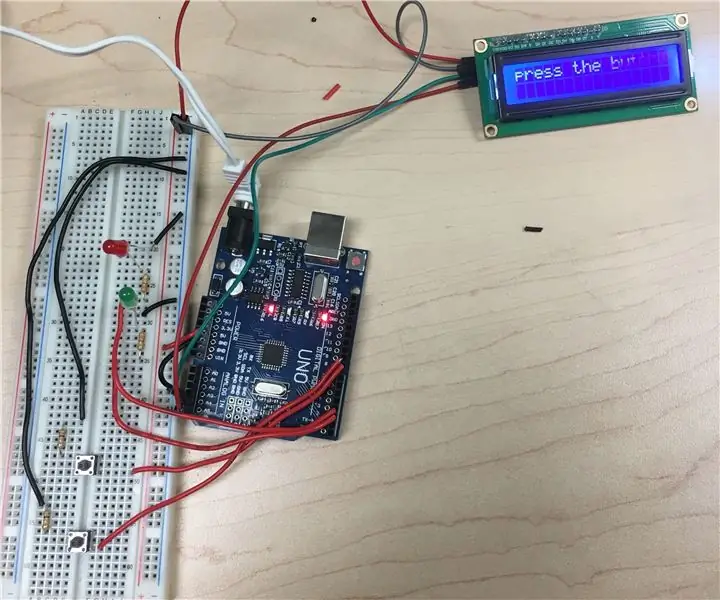

Arduino stopur ved hjælp af I2C LCD: 5 trin

Arduino stopur Brug af I2C LCD: I dette projekt vil jeg lære dig at bruge et LCD -display og en Arduino som et interaktivt stopur. Når dit projekt er færdigt med den angivne kode, skal det ligne billedet ovenfor. Gå til næste trin for at lære, hvor du skal starte

Sådan laver du et stopur ved hjælp af Arduino: 8 trin (med billeder)

Sådan laver du et stopur ved hjælp af Arduino: Dette er et meget simpelt Arduino 16*2 lcd display stopur ……….. Hvis du kan lide denne instruerbare, kan du abonnere på min kanal https://www.youtube.com /ZenoModiff

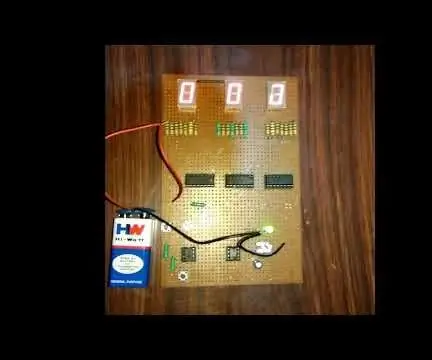

Sådan laver du digitalt stopur ved hjælp af 555: 3 trin

Sådan laver du digitalt stopur ved hjælp af 555: Jeg har lavet et simpelt stopur ved hjælp af 3 syv segment LED -display, hvoraf du først viser tiendedele sekunder en anden til anden og tredje i flere 10 krosekunder. Jeg brugte 555 timere i astabel tilstand som giver signal pr. 1 sekund til