Indholdsfortegnelse:

- Trin 1: Opsætning af et projekt i Vivado for Ernie

- Trin 2: Oprettelse af Ernies PWM i Vivado

- Trin 3: Oprettelse af Ernies TDOA i Vivado

- Trin 4: Indpakning og eksport af Ernie

- Trin 5: Bygning af Ernie

- Trin 6: Ernies første BSP

- Trin 7: FreeRTOS'ing Ernie

- Trin 8: Import af Ernies C -kode

- Trin 9: Debugging Ernie

- Trin 10: Gør Ernie autonom

- Trin 11: Gør Ernie Cute

Video: Sådan laver du Ernie: 11 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:26

Dette er en vejledning i, hvordan du opbygger Ernie, din autonome lyd efter robot, ved hjælp af et Zybo Board. Det vil dække, hvordan du: opretter et projekt i Vivado, opretter PWM-lignende servomotordrivere i FPGA, grænseflade med to lydsensorer, opretter en tidsforskel ved ankomst-IP, bruger freeRTOS og kører zyboen fra en batteripakke. Dette var vores sidste projekt for en Real Time Operating Systems -klasse (CPE 439) på Cal Poly SLO.

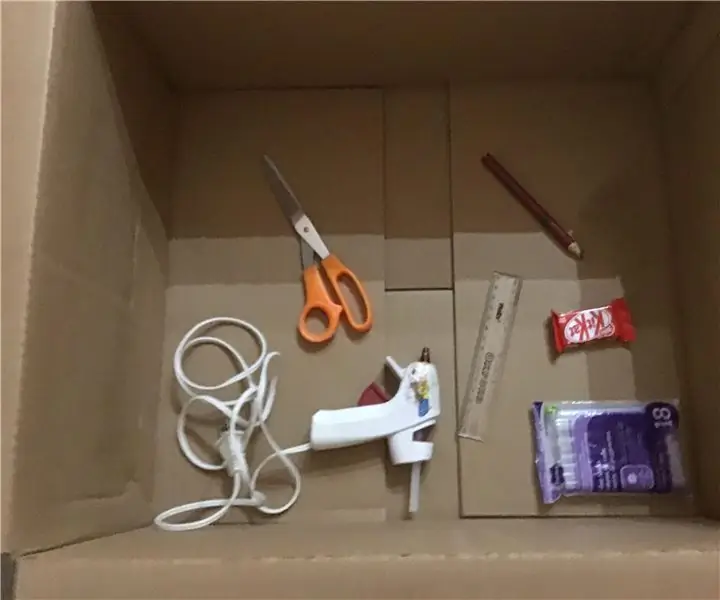

Udstyrsliste:

- 1 - ZYBO Zynq 7000 Development Board

- 2 - Parallax kontinuerlig rotationsservo

- 2 - Lydsensor (SparkFun lyddetektor)

- 1 - 5v litiumion USB -batteripakke (til bord)

- 4 - AA -batterier (til servoer)

- 1 - AA batteripakke (m/ 4 batteriåbninger)

- 1 - Micro USB -kabel

- 1 - Brødbræt

- mange - mandlige til mandlige ledninger

- 1 - Servokabinet

Softwarekrav:

- Xilinx Vivado Design Suite 2016.2

- Digilent Adept 2.16.1

Trin 1: Opsætning af et projekt i Vivado for Ernie

- En guide vil dukke op

- Klik på Næste

-

Næste navn på projektet

- Brug aldrig et projektnavn eller en biblioteksti, der har mellemrum i det !!!!!

- Dette bliver et RTL -projekt.

- Vi ønsker ikke at angive kilder

-

Ved at klikke på Næste kommer vi til siden Del. Vi bruger en ZYNQ XC7Z010-1CLG400C.

- Vivado har ikke Zybo opført som et af sine foruddefinerede tavler. Vælg: “dele”, og søg derefter efter xc7z010clg400-1.

- Hvis du ved en fejl vælger den forkerte del, kan du nemt skifte chips: Værktøjer -> Projektindstillinger -> Generelt og klik på prikkerne til højre for "Project Device"

-

Klik på Opret blokdesign.

Navngiv det design_1 for nu

- Du vil se en grøn bjælke, der siger Tilføj IP, klik på den.

-

Søg efter Zynq.

- Dobbeltklik på ZYNQ7 Processing System,

- Denne blok vises i vores blokdesign.

- Du vil se en grøn bjælke, der siger Run Block Automation, klik på den.

- Download zybo_zynq_def.xml herunder.

-

I Vivado skal du klikke på "Importer XPS -indstillinger" og vælge "zybo_zynq_def.xml"

Dette udfylder på forhånd Vivado-blokkonfigurationen med alle Zybo-plades indbyggede eksterne enheder og pin-tildelinger

-

Dobbeltklik på ZYNQ -blokken.

-

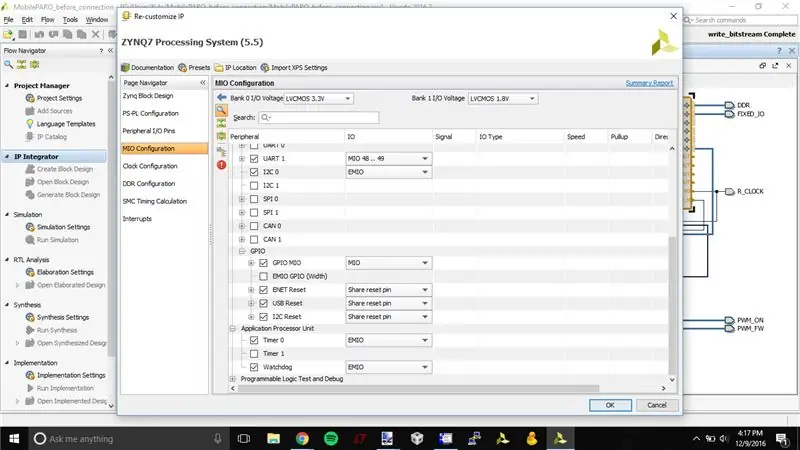

MIO -konfiguration

- Aktiver timer 0 (under applikationsprocessorenhed - billede 1)

- Aktiver vagthund (under applikationsprocessorenhed- billede 1)

- Aktiver GPIO-> GPIO MIO (under Application Processor Unit - billede 2)

- Aktiver GPIO-> ENET Reset (under I/O Peripherals- img 2)

-

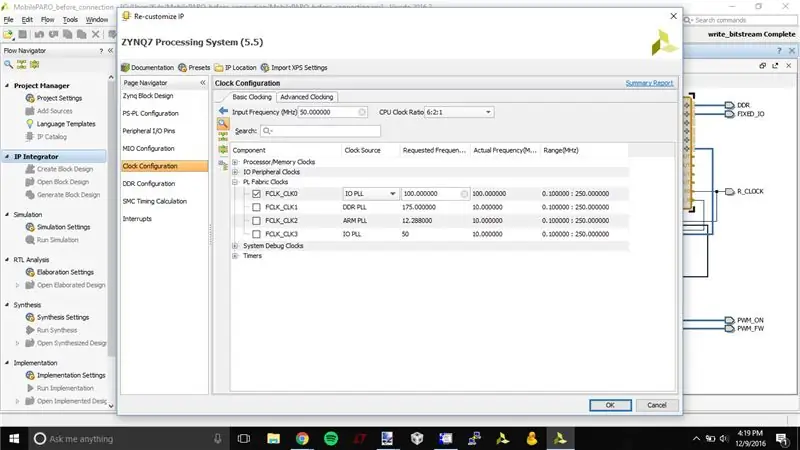

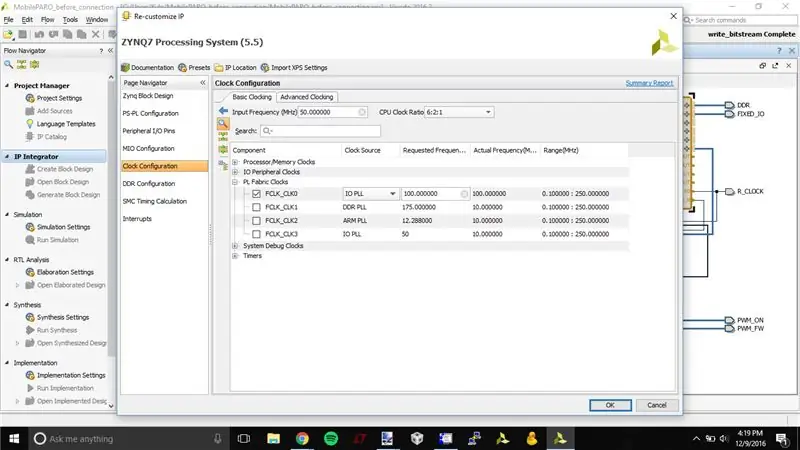

Urkonfiguration

Deaktiver FCLK0 (under PL Fabric Clocks - billede 3)

-

- Klik på Ok.

-

"Kør Block Automation" nu.

Der vil være nogle spørgsmål om signaler, sig OK

-

Klik på "Generer HDL Wrapper".

Vi vil gerne kopiere den genererede indpakning for at tillade brugerredigeringer

- Klik på OK.

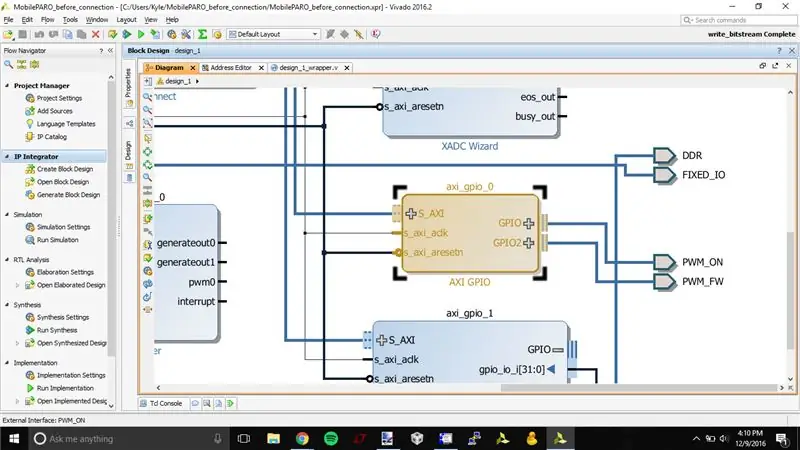

Trin 2: Oprettelse af Ernies PWM i Vivado

Dette trin genererer en PWM IP med input sendt via AXI -biblioteket.

-

Opret AXI GPIO-blok ved at højreklikke på baggrunden og klikke på "tilføj IP"

skriv "AXI_GPIO" i søgelinjen, og vælg denne pakke

-

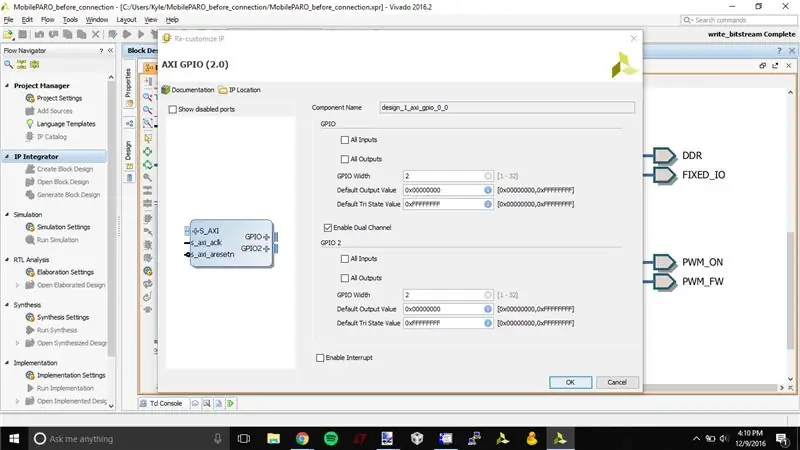

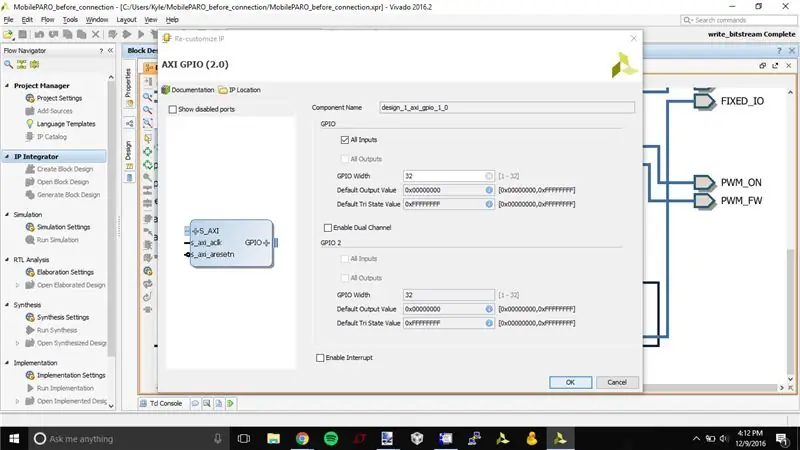

Tilpas IP igen ved at dobbeltklikke på den nye axi_gpio_0 blok

- under GPIO, skal du indstille GPIO -bredden til 2. Disse bits vil være PWM_ON -signalet til at drive hver PWM -modulinstans.

- klik på "aktiver dobbelt kanal"

- under GPIO 2, skal du indstille GPIO -bredden til 2. Disse bits vil være PWM_FW -signalet for at indstille retningen for hver PWM -modulinstans.

-

Højreklik på axi_gpio_0 outputporten mærket GPIO, og vælg "Lav ekstern"

- Klik på det nye output mærket GPIO, og naviger til fanen "egenskaber" i venstre værktøjslinje, og skift navnet til PWM_ON

- Klik på det nye output mærket GPIO2, og naviger til fanen "egenskaber" i venstre værktøjslinje, og skift navnet til PWM_FW

-

Vælg Kør forbindelsesautomatisering i det grønne banner over blokdiagrammet.

Hvis du tilslutter portene manuelt, konfigureres AXI -adresser muligvis ikke, hvilket kan føre til kommunikationsproblemer senere

-

I projektor i Flow Navigator skal du vælge projektleder -> Tilføj kilder for at oprette en ny brugerdefineret IP -blok

- vælg "tilføj eller opret designkilder", og tryk derefter på

- klik på "opret fil", skift filtype til "SystemVerilog", og skriv "pwm" i filnavnet, og klik derefter på OK

- klik på Afslut

-

ignorer vinduet Definer modul ved at trykke på OK (vi overskriver disse senere)

Hvis den spørger, om du er sikker, skal du klikke på Ja

-

I fanen Kilder skal du dobbeltklikke på pwm.sv (placeret i "Designkilder/design_1_wrapper")

Kopier/indsæt hele SystemVerilog -koden fra filen pwm.txt, der er vedhæftet nedenfor

Trin 3: Oprettelse af Ernies TDOA i Vivado

Dette trin genererer en TDOA IP, hvis output kan læses via AXI -biblioteket

-

Opret AXI GPIO-blok ved at højreklikke på baggrunden og klikke på "tilføj IP"

skriv "AXI_GPIO" i søgelinjen, og vælg denne pakke

-

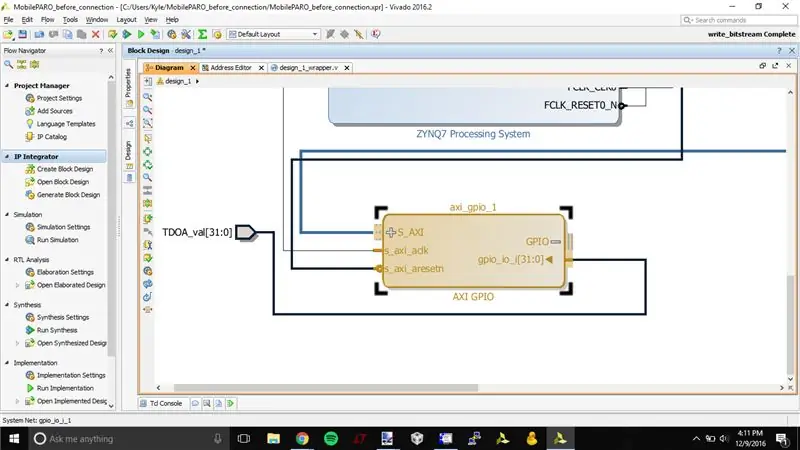

Tilpas IP igen ved at dobbeltklikke på den nye axi_gpio_1-blok

- under GPIO skal du markere afkrydsningsfeltet "Alle indgange" og indstille GPIO -bredden til 32. Denne bus er tidsforskellen ved ankomst mellem de to sensorer.

- inde i blokken axi_gpio_1 skal du klikke på + ud for GPIO -porten for at vise gpio_io_i [31: 0].

-

Højreklik på axi_gpio_1 outputporten mærket gpio_io_i [31: 0], og vælg "Make External"

Klik på det nye input mærket gpio_io_i [31: 0], og naviger til fanen "egenskaber" i venstre værktøjslinje, og skift navnet til TDOA_val

-

Vælg Kør forbindelsesautomatisering i det grønne banner over blokdiagrammet.

Hvis du tilslutter portene manuelt, konfigureres AXI -adresser muligvis ikke, hvilket kan føre til kommunikationsproblemer senere

-

I projektor i Flow Navigator skal du vælge projektleder -> Tilføj kilder for at oprette en ny brugerdefineret IP -blok

- vælg "tilføj eller opret designkilder", og tryk derefter på

- klik på "opret fil", skift filtype til "SystemVerilog", og skriv "tdoa" i filnavnfeltet, klik derefter på OK

- klik på Afslut

-

ignorer vinduet Definer modul ved at trykke på OK (vi overskriver disse senere)

Hvis den spørger, om du er sikker, skal du klikke på Ja

-

I fanen Kilder skal du dobbeltklikke på tdoa.sv (placeret i "Designkilder/design_1_wrapper")

Kopier/indsæt hele SystemVerilog -koden fra tdoa.txt -filen vedhæftet nedenfor

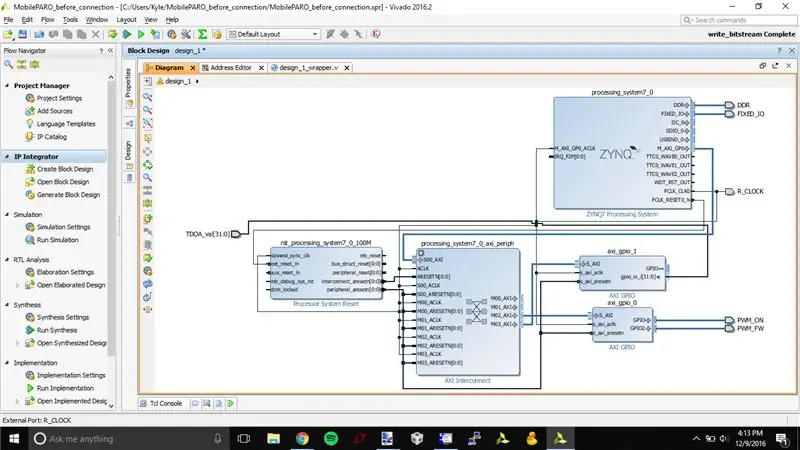

Trin 4: Indpakning og eksport af Ernie

- Kontroller, at blokdiagrammet ligner det vedhæftede skærmbillede

-

På fanen kilder skal du højreklikke på design_1.bd og vælge "Opret HDL-indpakning …"

- Vælg "Kopier genereret output for at tillade brugerredigeringer", og tryk derefter på "OK"

- Kopiér koden fra design_1_wrapper.txt vedhæftet nedenfor, og indsæt den i stedet for den genererede design_1_wrapper.v -kode

- gem design_1_wrapper.v

-

På fanen kilder skal du dobbeltklikke på filen ZYBO_Master.xdc under Begrænsninger/constrs1

- Kopiér koden fra ZYBO_Master.txt vedhæftet nedenfor, og indsæt den i stedet for den eksisterende ZYBO_Master.xdc -kode

-

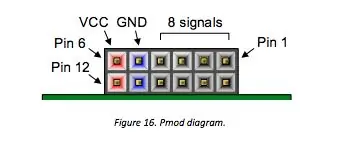

Bemærk følgende input/output pins:

- L15: PWM -signal til venstre motor (Pmod JA2 på Zybo)

- L14: PWM -signal til den højre motor (Pmod JA8 på Zybo)

- V12: gate -input fra lydsensor 1 (Pmod JE1 på Zybo)

- K16: gate -input fra lydsensor 2 (Pmod JE2 på Zybo)

-

I ruden Flow Navigator skal du klikke på "Generer Bitstream" under Program og fejlfinding

hvis du tror, det er gjort med det samme, er det sandsynligvis ikke. seriøst, lav noget te

-

Klik på Fil-> Eksport-> Generer hardware

Marker "Inkluder Bitstream", og tryk på OK

- Klik på Fil-> Start SDK

Trin 5: Bygning af Ernie

- Monter servoerne på servokabinettet.

-

Følg databladet for servoerne:

- slut jorden til servoer til jordstifter på Zybo's JA Pmod (se vedhæftede pinout -billede)

-

tilslut servostyrets power -pin til AA -batteriet

Vi fandt ud af, at når servoerne er forbundet med Zybo's Vdd, trækker brættet for meget strøm, hvilket får kortet til at nulstilles løbende

- tilslut indgangssignalstifterne til Zybo's passende udgangsstifter (venstre: JA2, højre: JA8)

- monter lydsensorerne på forsiden af chassiset, fremad, så de holdes så tæt på hinanden som muligt

-

brug lydsensorens tilslutningsguide til at integrere lydsensorerne

- led jorden og Vdd -benene på hver lydsensor til jorden og Vdd -benene på Zybo's JE Pmod (se vedhæftede pinout -billede)

- tilslut den venstre lydsensors Gate -pin til JE1

- tilslut den rigtige lydsensors Gate -pin til JE2

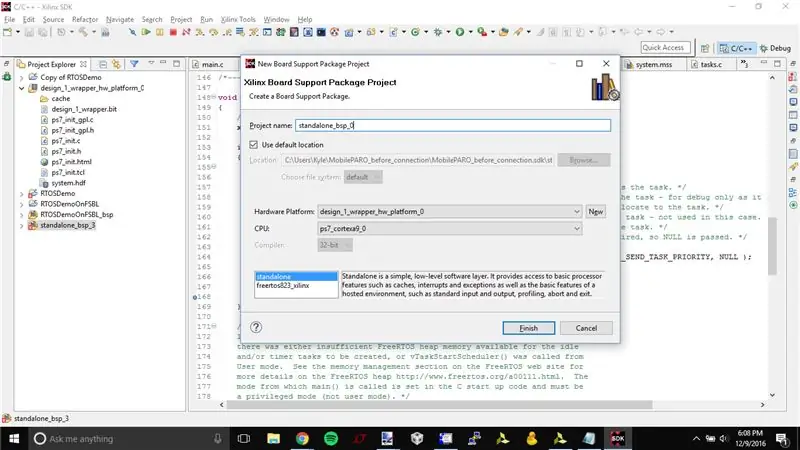

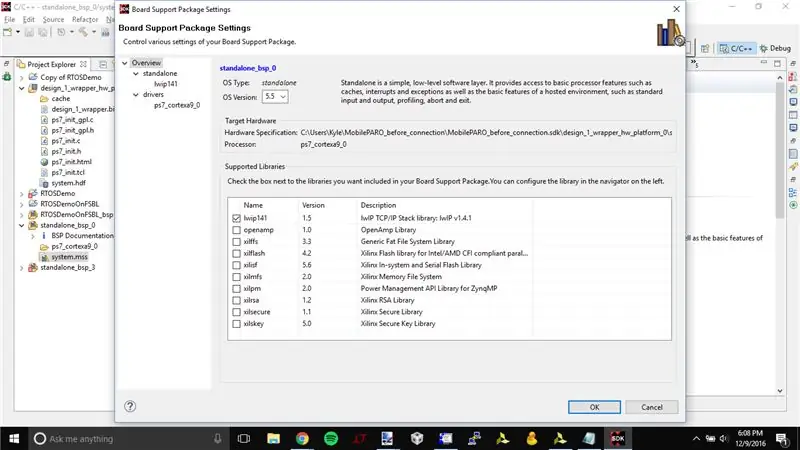

Trin 6: Ernies første BSP

-

Opret en BSP for at afslutte den platform, vi lige har oprettet.

Du kan få dette via File -> New -> Board Support Package

-

En guide vil dukke op for at hjælpe dig med at oprette BSP.

- Vi ønsker at binde denne BSP med vores platform, som vi lige har oprettet, så

- Hardwareplatform skal passe til den, vi lige har oprettet (se billede 1)

- Vores CPU vil være _0 CPU.

- Klik på Udfør

- Sørg for at markere lwip141 for inkludering med din bsp i det vindue, der dukker op (se billede 2)

Trin 7: FreeRTOS'ing Ernie

-

Download den seneste FreeRTOS -udgivelse fra Sourceforge.

Hvis overførslen er en eksekverbar fil, skal du køre den for at udtrække FreeRTOS -filerne til din projektmappe

- Hold den SDK åben, og klik på Fil -> Import.

- Vi vil klikke på Generelt-> Fra et eksisterende arbejdsområde, og derefter vil vi navigere til det sted, hvor vi downloadede FreeRTOS.

-

Vores demo vil være placeret i FreeRTOS/Demo/CORTEX_A9_Zynq_ZC702. Når vi vælger denne mappe, skal vi se tre projekter dukke op (vores kode (OS), det er BSP og HW -platformen).

KUN importere RTOSDemo til dit nuværende arbejdsområde

-

På alle "blå" mapprojekter ændrer den refererede BSP

- Højreklik og vælg "Skift refereret BSP."

- Vælg den BSP, du lige har oprettet til din Zybo

- Koderedigering i Xilinx’s SDK Blue -mapper er de faktiske kodeprojekter.

Trin 8: Import af Ernies C -kode

- I RTOSDemo/src -biblioteket skal du overskrive den eksisterende main.c med main.c -filen vedhæftet her.

- Kopier main_sound.c -fiilen til RTOSDemo/src -biblioteket.

Trin 9: Debugging Ernie

- Vælg Kør -> Debug -konfigurationer

- Opret en ny System Debugger -kørsel i venstre rude

-

I fanen Målopsætning,

vælg "Nulstil hele systemet", så både det og ps7_init vælges

-

Vælg nu fanen Applikation.

- Vælg "download -applikation"

- Indstil cortexa9_0 -kernen til "stop ved programindgang"

- Klik på Apply and Debug.

- Kontroller, at der ikke er fejl i fejlfindingsprocessen

- Hold godt øje med robotten, tryk på knappen Genoptag, indtil programmet kører uden at ramme nogen brudpunkter

- Robotten skal nu dreje og bevæge sig mod høje lyde. Yay!

Trin 10: Gør Ernie autonom

- Når dit projekt er klar til at gå (du kan køre uden problemer gennem fejlfindingsprogrammet) er du klar til at indlæse det i flash -hukommelsen på dit bord.

-

Opret det, der kaldes "first stage boot loader" (FSBL) -projektet og indeholder al den instruktion, som dit board skal bruge for at indlæse dine projektfiler (bitstrømmen og OS) ved opstart.

- Vælg: File-> New-> Application Project og det følgende vindue skal vises.

- Navngiv det, du ønsker (dvs. "FSBL")

- Sørg for, at hardware -platformen er den, du arbejder med

- Tryk på næste (Tryk ikke på Afslut)

- Vælg Zynq FSBL -skabelonen

- Klik på afslut.

- Når oprettelsesprocessen er fuldført, ved du, om alt fungerede, hvis du ser de følgende to nye mapper i vinduet Project Explorer.

-

Opret et boot -billede Nu skal du oprette Boot -billedet.

- Højreklik på din projektmappe (i dette tilfælde hedder min "RTOSDemo")

- Klik på "Opret boot -billede" i rullemenuen

-

Hvis alt er forbundet korrekt, ved projektet, hvilke filer det har brug for, og det følgende vindue ser ud som du ser nedenfor (nøglen er, at du har 3 partitioner under Boot image -sektionen, bootloaderen, din bitfil og dine projekter.elf -fil).

Hvis dette ikke er tilfældet, er der muligvis noget galt med, at dit projekt linker. Sørg for, at projektmapperne er knyttet til deres respektive BSP'er

- Klik på knappen "Opret billede"

-

Det sidste trin, der skal udføres i software, er nu at blinke dit tidligere oprettede billede til kortets hukommelse

- Vælg fra SDK's hovedværktøjslinje, vælg Xilinx Tools-> Program Flash Memory

- Sørg for, at den korrekte hardware -platform er valgt, og at billedfilens vej peger korrekt på. BIN -filen, der blev oprettet i det foregående trin.

- Vælg "qspi single" fra Flash -typen

- Marker "Verificer efter flash" for at sikre integriteten, men det er ikke nødvendigt

- Konfigurer dit kort Endelig skal du sikre dig, at kortene til programmeringsfunktionen (JP5) er korrekt indstillet til at vælge at starte fra qspi (som indeholder det, du lige har blinket), når BootROM køres.

- Nu skal du blot tænde for enheden og sikre, at "Logic Configuration Done LED" (LED 10) lyser grønt.

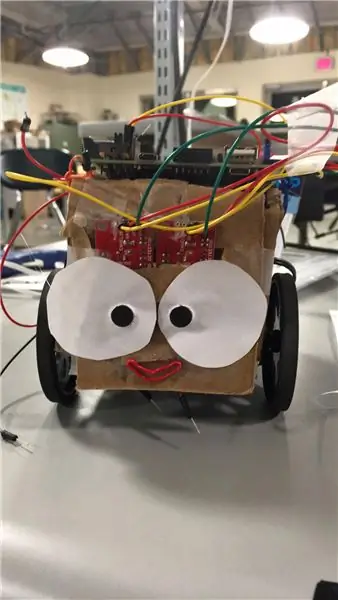

Trin 11: Gør Ernie Cute

- Pels

- Masser af pels

- Store øjne!

- … høj hat

Anbefalede:

Sådan laver du en trådløs dåse-telefon! (Arduino Walkie Talkie): 7 trin (med billeder)

Sådan laver du en trådløs dåse-telefon! (Arduino Walkie Talkie): Lige forleden var jeg midt i et meget vigtigt telefonopkald, da min banantelefon holdt op med at fungere! Jeg var så frustreret. Det er sidste gang, jeg savner et opkald på grund af den dumme telefon! (Set i bakspejlet er jeg måske blevet lidt for sur i

Sådan laver du en lineær aktuator: 3 trin

Sådan laver du en lineær aktuator: Lineære aktuatorer er maskiner, der konverterer rotation eller enhver bevægelse til et skub eller en trækbevægelse. Her skal jeg lære dig, hvordan du laver en elektrisk lineær aktuator ved hjælp af husholdnings- og hobbyobjekter. Det er meget meget billigt

Sådan laver du solopladeligt lys: 8 trin

Sådan laver du solopladeligt lys:

Sådan laver du LED -terning - LED Cube 4x4x4: 3 trin

Sådan laver du LED -terning | LED Cube 4x4x4: En LED Cube kan opfattes som en LED -skærm, hvor enkle 5 mm LED’er spiller rollen som digitale pixels. En LED -terning giver os mulighed for at skabe billeder og mønstre ved at bruge konceptet om et optisk fænomen kendt som persistens of vision (POV). Så

Sådan laver du en delt skærmvideo med fire trin: 4 trin (med billeder)

Sådan laver du en delt skærmvideo med fire trin: Vi ser ofte en samme person vise sig i en scene to gange i et tv -afspilning. Og så vidt vi ved, har skuespilleren ikke en tvillingebror. Vi har også set, at to sangvideoer er sat på en skærm for at sammenligne deres sangevner. Dette er kraften i spl