Indholdsfortegnelse:

- Trin 1: ADC -arkitektur

- Trin 2: Intern kredsløb

- Trin 3: Eksternt kredsløb

- Trin 4: I2C Læs vejledningen

- Trin 5: Resultater

Video: Sådan laver du ADC Current Sense: 5 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:26

I denne instruktionsbog beskriver vi, hvordan man implementerer en 8-bit analog-til-digital-konverter (ADC) i SLG46855V, der kan registrere belastningsstrøm og grænseflade med en MCU via I2C. Dette design kan bruges til forskellige aktuelle registreringsapplikationer såsom ammetre, fejldetekteringssystemer og brændstofmålere.

Nedenfor beskrev vi de nødvendige trin for at forstå, hvordan løsningen er blevet programmeret til at skabe ADC's aktuelle forstand. Men hvis du bare vil få resultatet af programmeringen, skal du downloade GreenPAK -software for at se den allerede gennemførte GreenPAK -designfil. Tilslut GreenPAK Development Kit til din computer, og tryk på programmet for at skabe ADC -aktuel følelse.

Trin 1: ADC -arkitektur

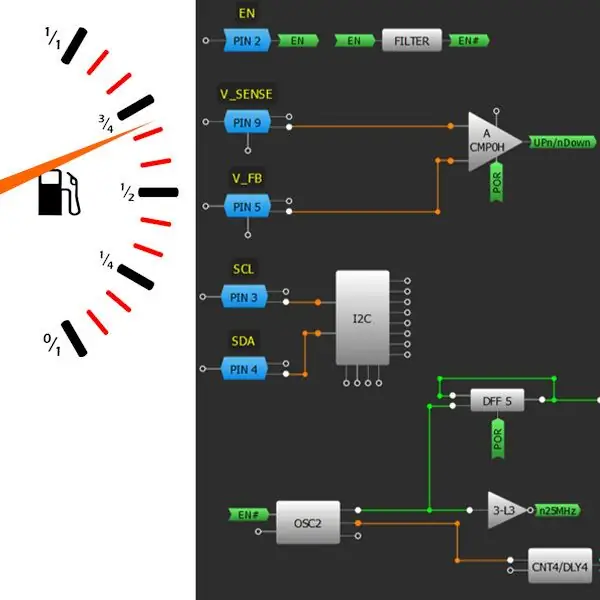

ADC består hovedsageligt af en analog komparator og en Digital-til-analog konverter (DAC). Komparatoren registrerer indgangsspændingen mod DAC -udgangsspændingen og kontrollerer efterfølgende, om DAC -inputkoden skal øges eller reduceres, således at DAC -udgangen konvergerer til indgangsspændingen. Den resulterende DAC -inputkode bliver den digitale ADC -udgangskode.

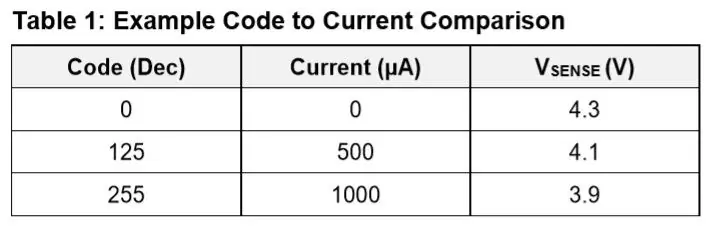

I vores implementering opretter vi en DAC ved hjælp af et pulsbreddemodulation (PWM) styret modstandsnetværk. Vi kan nemt oprette en præcis digitalt styret PWM -output ved hjælp af GreenPAK. PWM, når den filtreres, bliver vores analoge spænding og fungerer således som en effektiv DAC. En klar fordel ved denne fremgangsmåde er, at det er let at indstille de spændinger, der svarer til nulkode og fuld skala (tilsvarende forskydning og forstærkning) ved blot at justere modstandsværdier. For eksempel vil en bruger ideelt aflæse nulkode fra en temperatursensor uden strøm (0 µA) svarende til 4,3 V og fuldskala-kode ved 1000 µA svarende til 3,9 V (tabel 1). Dette implementeres let ved blot at angive et par modstandsværdier. Ved at lade ADC -området matche sensorintervallet, gør vi størst brug af ADC -opløsningen.

Et designovervejelse for denne arkitektur er, at en intern PWM -frekvens skal være meget hurtigere end ADC -opdateringshastigheden for at forhindre underdæmpet adfærd i dens kontrolsløjfe. I det mindste bør det være længere end ADC -datatællerens ur divideret med 256. I dette design er ADC -opdateringsperioden sat til 1,3312 ms.

Trin 2: Intern kredsløb

Den fleksible ADC er baseret på designet præsenteret i Dialog Semiconductor AN-1177. Urhastigheden øges fra 1 MHz til 12,5 MHz for at klokke ADC -tælleren, da SLG46855 har et 25 MHz -ur til rådighed. Dette giver en meget hurtigere opdateringshastighed for finere prøveopløsning. LUT -uret til ADC -datauret ændres, så det vil passere gennem 12,5 MHz -signalet, når PWM DFF er lav.

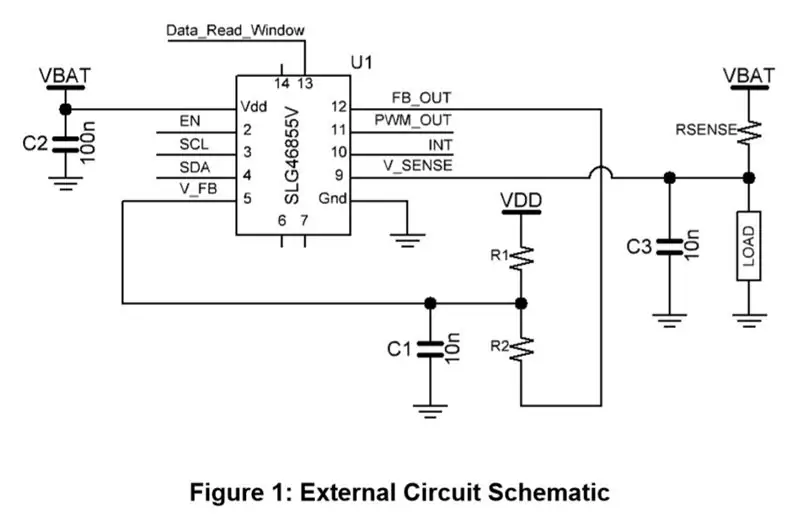

Trin 3: Eksternt kredsløb

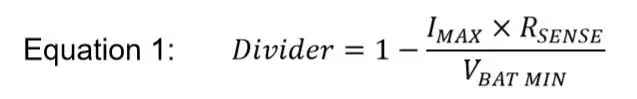

En ekstern modstand og kondensatornetværk bruges til at konvertere en PWM til en analog spænding som vist i kredsløbsskemaet i figur 1. Værdierne beregnes for maksimal opløsning for den maksimale strøm, enheden vil registrere. For at opnå denne fleksibilitet tilføjer vi modstande R1 og R2 parallelt med VDD og jord. En modstandsdeler deler VBAT ned til den lave side af spændingsområdet. Opdelingsforholdet for et forventet minimum VBAT kan løses ved hjælp af ligningen 1.

Trin 4: I2C Læs vejledningen

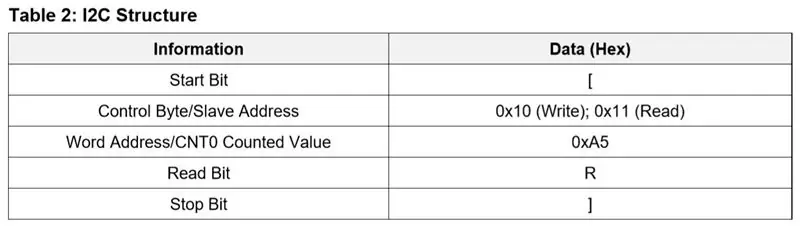

Tabel 1 beskriver I2C -kommandostrukturen til at læse data tilbage i CNT0 tilbage. I2C -kommandoerne kræver en startbit, kontrolbyte, ordadresse, læsebit og stopbit.

Et eksempel I2C -kommando til at læse CNT0 -tællingsværdien tilbage er skrevet nedenfor:

[0x10 0xA5] [0x11 R]

Den optalte værdi, der læses tilbage, er ADC -kodeværdien. Som et eksempel er en Arduino -kode inkluderet i ZIP -filen i denne applikationsnote på Dialogs websted.

Trin 5: Resultater

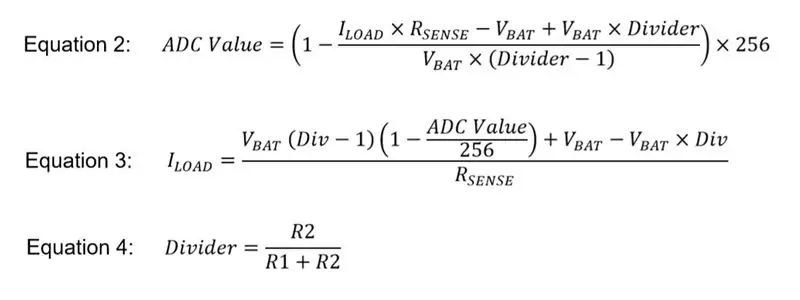

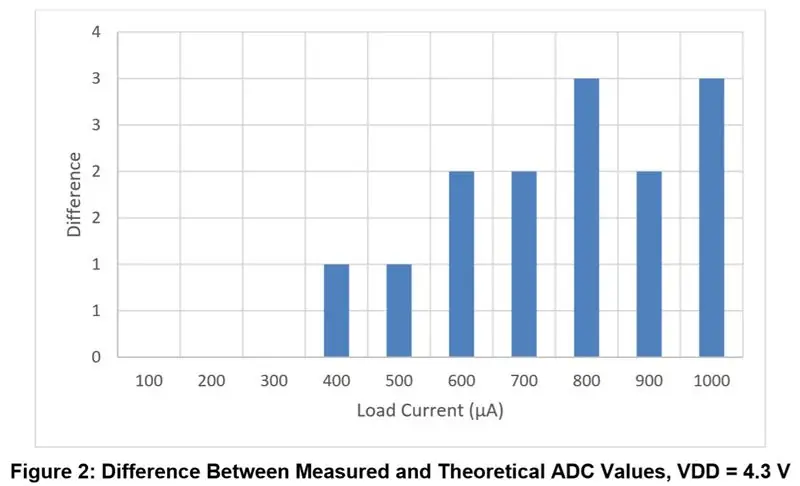

For at teste nøjagtigheden af ADC nuværende følelsesdesign blev måleværdierne ved en given belastningsstrøm og VDD -niveau sammenlignet med en teoretisk værdi. De teoretiske ADC -værdier blev beregnet med ligningen 2.

ILOAD, der korrelerer med en ADC -værdi, findes med ligningen 3.

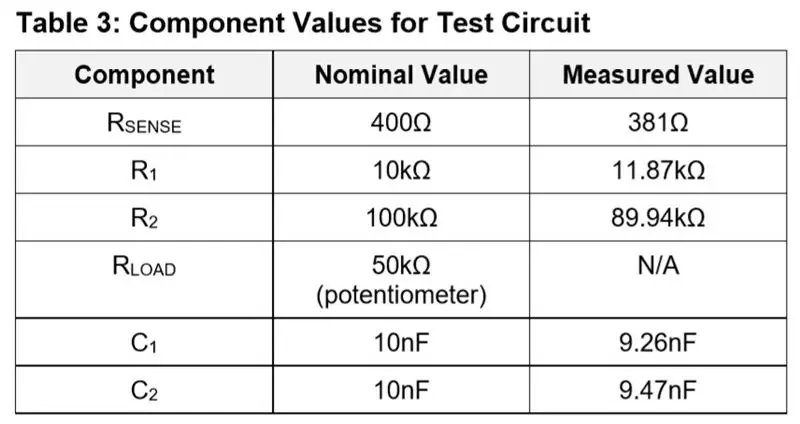

For de følgende resultater brugte jeg disse komponentværdier vist i tabel 3.

Opløsningen af ADC -værdien til ILOAD -konvertering kan beregnes ved hjælp af ligning 3 med de målte værdier i tabel 2 og ADC -værdien indstillet til 1. Med en VBAT på 3,9 V er opløsningen 4,96 µA/div.

For at optimere ADC -strømfølerkredsløbet til et minimum VDD -niveau på 3,6 V med en maksimal strøm på 1100 µA og en 381 Ω følermodstand, ville den ideelle divider -koefficient være 0,884, baseret på ligning 1. Med værdierne i tabel 2, har den faktiske divider en divider koefficient på 0,876. Da dette er lidt mindre, giver det mulighed for et lidt større belastningsstrøminterval, så ADC -værdierne er tæt på hele området, men ikke vil flyde over. Den faktiske dividerværdi beregnes med ligningen 4.

Ovenfor (figur 2-6, tabeller 4-6) er målingerne foretaget af kredsløbet ved tre spændingsniveauer: 4,3 V, 3,9 V og 3,6 V. Hvert niveau viser en graf, der viser forskellen mellem de målte og teoretiske ADC-værdier. Teoretiske værdier afrundes til det nærmeste hele heltal. Der er en oversigtsgraf til sammenligning af forskellene ved de tre spændingsniveauer. Bagefter er der en graf, der viser sammenhængen mellem de teoretiske ADC -værdier og belastningsstrøm ved de forskellige spændingsniveauer.

Konklusion

Enheden blev testet ved tre spændingsniveauer: 3,6 V, 3,9 V og 4,3 V. Omfanget af disse spændinger modellerer et fuldt lithiumionbatteri, der aflades til sit nominelle niveau. Af de tre spændingsniveauer observeres det, at enheden typisk var mere præcis ved 3,9 V for det valgte eksterne kredsløb. Forskellen mellem de målte og teoretiske ADC -værdier var kun 1 decimalværdi fra ved belastningsstrømme på 700 - 1000 µA. Ved det givne spændingsområde var de målte ADC -værdier 3 decimaler over de nominelle forhold i værste fald. Yderligere justeringer af modstandsdeleren kan foretages for at optimere forskellige VDD -spændingsniveauer.

Anbefalede:

Sådan laver du en trådløs dåse-telefon! (Arduino Walkie Talkie): 7 trin (med billeder)

Sådan laver du en trådløs dåse-telefon! (Arduino Walkie Talkie): Lige forleden var jeg midt i et meget vigtigt telefonopkald, da min banantelefon holdt op med at fungere! Jeg var så frustreret. Det er sidste gang, jeg savner et opkald på grund af den dumme telefon! (Set i bakspejlet er jeg måske blevet lidt for sur i

Sådan laver du en lineær aktuator: 3 trin

Sådan laver du en lineær aktuator: Lineære aktuatorer er maskiner, der konverterer rotation eller enhver bevægelse til et skub eller en trækbevægelse. Her skal jeg lære dig, hvordan du laver en elektrisk lineær aktuator ved hjælp af husholdnings- og hobbyobjekter. Det er meget meget billigt

Sådan laver du solopladeligt lys: 8 trin

Sådan laver du solopladeligt lys:

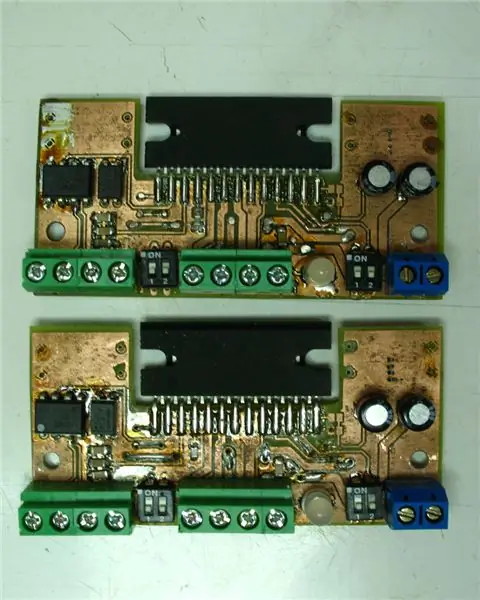

Sådan laver du en HIGH Current Driver til en trinmotor: 5 trin

Sådan laver du en HØJ nuværende driver til en trinmotor: her vil vi se, hvordan du laver en trinmotor driver ved hjælp af Toshibas TB6560AHQ controller. Dette er en fuldt udstyret controller, der kun har brug for 2 variabler som input, og det gør alt arbejdet. Da jeg havde brug for to af disse, har jeg lavet dem begge ved hjælp af

Sådan laver du en delt skærmvideo med fire trin: 4 trin (med billeder)

Sådan laver du en delt skærmvideo med fire trin: Vi ser ofte en samme person vise sig i en scene to gange i et tv -afspilning. Og så vidt vi ved, har skuespilleren ikke en tvillingebror. Vi har også set, at to sangvideoer er sat på en skærm for at sammenligne deres sangevner. Dette er kraften i spl