Indholdsfortegnelse:

- Trin 1: Konfigurer Zynq programmerbar logik til sender

- Trin 2: Konfigurer Zynq programmerbar logik til modtager

- Trin 3: Opsætning af VDMA -driver

- Trin 4: Konfigurer Nanorouter -netværk

- Trin 5: Opsætning af Zynq -behandlingssystem til dataoverførsel via Ethernet

- Trin 6: Opsætning af Zynq -behandlingssystem til datamodtagelse via Ethernet

- Trin 7: Tilslut dine Zybo -plader til HDMI -kilden og HDMI -vasken

- Trin 8: Alternative ideer til forbedring

- Trin 9: Tilgængelighed

Video: WIDI - Trådløs HDMI ved hjælp af Zybo (Zynq Development Board): 9 trin (med billeder)

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:28

Har du nogensinde ønsket, at du kunne slutte dit tv til en pc eller bærbar computer som en ekstern skærm, men ville ikke have alle de irriterende ledninger i vejen? I så fald er denne tutorial lige noget for dig! Selvom der er nogle produkter ude, der opnår dette mål, er et DIY -projekt meget mere tilfredsstillende og potentielt billigere.

Dette koncept adskiller sig fra produkter som chromecast, da det er beregnet til at tage stedet for et HDMI -kabel, der forbinder til en skærm i stedet for at være en streaming -enhed.

Vores projekt blev oprettet som et afsluttende projekt til et Real Time Operating Systems -kursus ved California State Polytechnic University, San Luis Obispo.

Målet med projektet er at bruge to Digilent Zybo-kort til at fungere som den trådløse kommunikationsgrænseflade mellem en HDMI-senderenhed (pc, blu-ray osv.) Til en HDMI-modtagerenhed (Desktop Monitor, Projector, TV osv.).

Den ene Digilent Zybo tilsluttes via HDMI til sendeenheden, og den anden tilsluttes via HDMI til den modtagende enhed.

Den trådløse kommunikation foretages ved hjælp af et trådløst lokalnetværk, der er dedikeret til senderen og modtageren, uden at blive routet gennem en hjemmrouter eller anden sådan enhed. Det trådløse modul, der bruges til dette projekt, er tplink wr802n nanorouter, hvoraf det ene fungerer som et adgangspunkt til etablering af netværket og det andet til at fungere som en klient for at oprette forbindelse til netværket. Hver nanorouter forbindes via ethernet -kabel til enten Zybo -kort. Når de er forbundet til disse routere, vil enhederne kommunikere via TCP, som om de var forbundet med et enkelt ethernet -kabel (hvilket betyder, at den eneste konfiguration, der er nødvendig for at etablere en forbindelse, er klientens IP -adresse).

Selvom målet med projektet var at lette en strøm af 1080x720 video @ 60Hz, var dette ikke muligt på grund af begrænsninger i båndbredde i det trådløse netværk og manglen på realtidskomprimering af video for at reducere de data, der kræves for at sende. I stedet fungerer dette projekt som rammen for fremtidig udvikling for at nå dette mål, da det har stærkt begrænsede begrænsninger i billedhastighed til korrekt at streame HDMI -data efter hensigten.

Projektkrav:

2x Digilent Zybo Development Boards (skal have mindst en HDMI -port)

2x HDMI kabler

2x microusb -kabler (til tilslutning af Zybo til pc til udvikling)

2x tplink wr802n nanorouters (inklusive adtl. 2x microusb- og stikkontakter til vægudtag)

2x ethernet kabler

*** Bemærk: Denne vejledning forudsætter kendskab til Vivado designsuite og erfaring med at oprette et nyt projekt og blokdesign. ***

Trin 1: Konfigurer Zynq programmerbar logik til sender

Vores tilgang til at udvikle senderens programmerbare logik var at udføre en hdmi-til-hdmi-gennemgang fra pc til at overvåge ved hjælp af to Video Direct Memory Access (VDMA) blokke, en til skrive og en til læsning.

Begge er valgt til frit løbende, 3 frame-buffer-tilstand (0-1-2). Da videokernen er optimeret til 60 billeder i sekundet, betyder det, at VDMA vil skrive eller læse til en ny ramme hver 16,67 ms i denne rækkefølge: 0, 1, 2, 0, 1, 2, 0, 1, 2. DDR -hukommelseslokationerne for hver ramme er forskellige for de to VDMA'er, fordi de ikke længere er synkroniseret med hinanden. I stedet bruges en hardware -timer (TTC1), konfigureret til 60 Hz, til at synkronisere bevægelsen af data mellem de to hukommelsessteder.

Billedet ovenfor viser 3 rammer, deres dimensioner og mængden af hukommelse hver kræver (til højre for rammen). Hvis vi tildeler skrive -VDMA til disse hukommelsesplaceringer, kan vi tildele de læste VDMA -hukommelsesplaceringer ud over dette sæt, f.eks. Startende med 0x0B000000. Hver ramme består af 1280*720 pixels, og hver pixel består af 8 bits rød, grøn og blå i alt 24 bit. Det betyder, at en ramme består af 1280*720*3 bytes (2,76 MB).

Inde i timeren vil IRQ, som er beskrevet i VDMA -driveropsætningen, håndtere kopiering af data mellem de to VMDA -hukommelsesplaceringer. VDMA giver en markør til den aktuelle ramme, der skrives til eller læses fra. Rammen er repræsenteret af en særlig grå kode, som konverteres til software. De grå kode definitioner for en 3 frame-buffer konfiguration findes i AXI VDMA Product Guide i tillæg C.

Dette giver os mulighed for at kopiere det indhold, der skrives til hukommelsen uden at læse fra en ramme, der i øjeblikket skrives til.

*** Bemærk, at den læste VDMA ikke bruges, når der sendes data på tværs af det trådløse netværk. Det eneste formål er at kontrollere, at kopiering af hukommelse fungerer korrekt fra skrive -VMDA. Den læste VMDA bør deaktiveres. ***

Her er trinene til oprettelse af senderens designblok:

- Når du opretter et nyt projekt, er det en god idé at tildele en chip eller et bord til projektet. Dette link beskriver, hvordan du tilføjer nye tavlefiler til Vivado -biblioteket og knytter det korrekte kort til dit projekt. Det vil være praktisk, når du tilføjer Processing System -blokken og overgår fra hardware til software (SDK -side).

-

Tilføj følgende blokke:

- dvi2rgb

- Video ind til Axi4-stream

- Timing Controller

- axi4-stream til vid ud

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Urguide

- Konstant

- Zynq Processing System

- Når du tilføjer behandlingssystemet, skal du klikke på "Kør blokautomatik" fra den øverste grønne bjælke og sikre dig, at indstillingen "Anvend forudindstilling af bord" er valgt. Lad alt andet stå som standard.

- Billeder af hvert blokkonfigurationsvindue findes i billederne ovenfor. Hvis du ikke kan se et billede for et bestemt vindue, skal du bare lade det være som standard.

-

Begynd at konfigurere Zynq -behandlingssystemet:

- Aktiver M AXI GP0-grænseflade i PS-PL-konfiguration AXI Non Secure Enable GP Master AXI

- Aktiver både HP0 og HP1 i PS-PL-konfiguration HP Slave AXI-grænseflade

- I MIO -konfiguration Sørg for, at ENET0 er aktiveret under I/O -periferiudstyr, derefter Application Processor Unit, aktiver Timer0

- I Clock Configuration PL Fabric Clocks skal du aktivere FCLK_CLK0 og indstille til 100 MHz.

- Klik på Ok

- Inden du klikker på "Kør forbindelsesautomatisering", skal du sørge for at forbinde videoblokkene som vist i TX -blokdesignbilledet ovenfor. Du vil omdøbe konstanten til VDD og indstille værdien til 1. Tilslut videoblokkene i overensstemmelse hermed.

- Gør HDMI TMDS -uret og datastifterne eksterne på rgb2dvi- og dvi2rgb -blokke

- Opret en input- og outputport til hot plug -detekteringssignalet (HPD) og tilslut dem sammen, disse er defineret i begrænsningsfilen

-

Pixel -uret gendannes fra TMDS_Clk_p, som oprettes i begrænsningsfilen. Dette vil være 74,25 MHz i overensstemmelse med 720p opløsning. Det er vigtigt at forbinde pixeluret (fra dvi2rgb -blokken) til følgende pins:

- vid_io_in_clk (vid ind til axi stream blok)

- vid_io_out_clk (axi stream til vid out blok)

- clk (Timing Controller)

- PixelClk (rgb2dvi)

- *** Bemærk: For at aktivere pixelurgendannelsen skal HDMI rx- og tx -stik i øjeblikket sættes i en aktiv kilde/vask. En vej udenom dette er at adskille video rx og tx blokke til forskellige ur domæner (med andre ord, generer et nyt 74,25 MHz ur til feed til tx blokken). ***

- Konfigurer derefter urguiden, så du har en 100 MHz input (global bufferkilde) og 3 output ure @ 50 MHz (AXI-Lite ur), 150 MHz (AXI4-Stream ur), 200 MHz (dvi2rgb RefClk pin).

- Slut FCLK_CLK0 -behandlingssystemets pin til urguidenes input

- Klik på dette tidspunkt på "Kør forbindelsesautomatisering" fra den grønne bjælke øverst i designvinduet. Det er en god idé at gøre dette for en blok ad gangen og følge TX -blokdesignbilledet ovenfor.

- Værktøjet vil forsøge at tilføje AXI-forbindelsen, der fungerer som master/slave-forbindelsen for de blokke, der bruger AXI-Lite-bussen (VDMA'er og GPIO'er).

- Det tilføjer også AXI SmartConnect, der fungerer som master/slave-forbindelse til AXI4-Stream- og High Performance-processorinterfaces, der bruges af VDMA (Stream to Memory Map og vice versa).

- Værktøjet tilføjer også en nulstilling af processorsystem. Sørg for, at dette kun er forbundet til VDMA'er, GPIO'er og processorrelaterede blokke. Tilslut den ikke til nogen videoblokke (dvs. dvi2rgb, timing controller, vid til stream osv.)

- Når forbindelsesautomatisering er fuldført, skal du kontrollere, at forbindelserne matcher forbindelsen til TX -blokdesignbilledet. Du vil bemærke en ekstra System ILA -blok, der ikke er blevet nævnt. Dette er kun til fejlfinding og er ikke nødvendigt i øjeblikket. Den bruger 150M processor -nulstilling, så det er heller ikke nødvendigt. Overalt ser du små grønne "fejl" på busser, det er på grund af ILA og kan ignoreres.

- Det sidste trin er at højreklikke på blokdesignet i projektkildetræet og vælge "Opret HDL Wrapper." Hvis du planlægger at tilføje logik til omslaget, bliver det overskrevet hver gang dette vælges.

- Se afsnittet VDMA Driver Setup for oplysninger om SDK -siden.

Ure og nulstillinger

Jeg har fundet ud af, at de vigtigste aspekter ved ethvert programmerbart logisk projekt er omhyggelig overvejelse af urdomæner og nulstillingssignaler. Hvis de er korrekt konfigureret, har du et godt forsøg på at få dit design til at fungere.

Pixel ur og timing låst

For at kontrollere, at visse signaler er aktive, er det en god idé at binde disse signaler til lysdioder (ure, nulstillinger, låse osv.). To signaler, som jeg fandt nyttige at spore på senderkortet, var pixeluret og det "låste" signal på AXI4-Stream til video-ud-blokken, som fortæller dig, at videotimingen er blevet synkroniseret med timing-controlleren og videokilden data. Jeg har tilføjet en vis logik til designblokomslaget, der sporer pixeluret ved hjælp af PixelClkLocked -signalet på dvi2rgb -blokken som en nulstilling. Jeg har vedhæftet filen som hdmi_wrapper.v her. Begrænsningsfilen er også vedhæftet her.

Trin 2: Konfigurer Zynq programmerbar logik til modtager

Den programmerbare logikblok til modtageren er enklere. Den vigtigste forskel, bortset fra de manglende hdmi -inputblokke, er fraværet af et gendannet pixelur. Af den grund er vi nødt til at generere vores egen fra urguiden. Dette design skal udføres i et separat projekt fra senderen. Til vores formål fulgte modtagerprojektet Zybo 7Z-20-kortet, mens senderen fulgte Z7-10-kortet. FPGA'erne på tavlerne er forskellige, så … vær forsigtig.

Her er trinene til at oprette modtagerens designblok:

-

Tilføj følgende ip -blokke til dit design:

- Timing Controller

- AXI4-Stream til videoudgang

- RGB til DVI

- AXI VDMA

- AXI GPIO

- Forarbejdningssystem

- Urguide

- Konstant (VDD indstillet til 1)

- Følg det samme mønster til konfiguration af disse blokke som senderen. Billeder til de bemærkelsesværdige forskelle i konfiguration er blevet inkluderet her. De andre forbliver de samme som senderen.

- Konfigurer VDMA'en for dette design som kun læskanal. Deaktiver skrivekanalen.

-

Urguiden skal konfigureres til følgende output:

- clk_out1: 75 MHz (pixelur)

- clk_out2: 150 MHz (strømur)

- clk_out3: 50 MHz (axi-lite ur)

- Tilslut videoblokke som vist i RX -blokdesignbilledet.

- Kør derefter forbindelsesautomatiseringen, som tilføjer AXI Interconnect, AXI SmartConnect og System Reset -blokke og forsøger at foretage de relevante forbindelser. Gå langsomt her for at sikre, at det ikke udfører uønskede forbindelser.

- Gør HDMI TMDS -uret og datastifterne eksterne på rgb2dvi -blokken

- Intet behov for hot plug -signal på dette design.

Trin 3: Opsætning af VDMA -driver

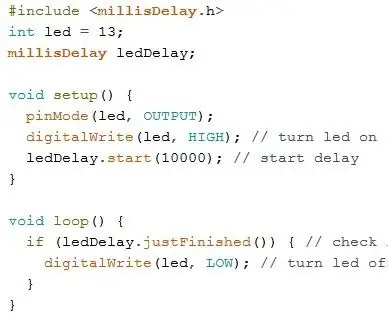

Opsætning af de forskellige blokke, der konfigureres via AXI-Lite-grænsefladen, udføres bedst ved at bruge demoprojekter, der følger med BSP som reference. Efter at have eksporteret designhardwaren og lanceret SDK fra Vivado, vil du gerne tilføje en ny board -supportpakke og inkludere lwip202 -biblioteket i vinduet BSP -indstillinger. Åbn system.mss -filen fra BSP, og du vil se de perifere drivere til stede fra dit blokdesign. Indstillingen "Importeksempler" lader dig importere demoprojekter, der anvender disse eksterne enheder og dermed vise dig, hvordan du konfigurerer dem i software ved hjælp af de tilgængelige Xilinx -drivere (se vedhæftede billede).

Dette var den metode, der blev brugt til at konfigurere VDMA, Timer & Interrupt og GPIO. Kildekoden til både transmission og modtagelse er inkluderet her. Forskellene er næsten udelukkende i main.c.

*** BEMÆRK: Da systemet ikke er fuldt funktionsdygtigt på tidspunktet for at skrive denne vejledning, inkluderer kildekoden i dette afsnit ikke den trådløse netværkskode. Flere fejl skal rettes som følge af at kombinere videokerneoverførsels-/modtageprojekter med netværkssend/modtag -projekter. Derfor behandler denne vejledning dem separat hver for sig. ***

TX Interrupt Handler -funktion (IRQHandler)

Denne funktion læser de grå koder, der leveres af både læse- og skrive -VDMA'erne via GPIO -blokke. De grå koder konverteres til decimal og bruges til at vælge rammebasens hukommelsesplacering for den aktuelle ramme. Den kopierede ramme er den forrige ramme til den, som VDMA skriver til (f.eks. Hvis VDMA skriver til ramme 2, kopierer vi ramme 1; hvis vi skriver til ramme 0, pakker vi ind og læser fra ramme 2).

Funktionen optager kun hver 6. ramme for at reducere billedhastigheden til 10 Hz frem for 60 Hz. Den øvre grænse for netværket er 300 Mbps. Ved 10 billeder i sekundet kræves en båndbredde på 221,2 Mbps.

Kommentering/fjernelse af kommentarer til to linjer i denne funktion giver brugeren mulighed for at skifte til HDMI-passthru-tilstand til fejlfinding/testformål (koden kommenteres for at angive de relevante linjer). Det kopierer i øjeblikket rammen til et hukommelsessted, der bruges af ethernet -koden.

RX Interrupt Handler -funktion (IRQHandler)

Denne funktion ligner meget TX -funktionen, men den kopierer fra en 2 -buffer FIFO, der bruges af ethernet til at skrive indgående data til. Ethernet -koden angiver, hvilken ramme der skrives til af FIFO, data kopieres fra den modsatte ramme. Dataene kopieres til rammen direkte bag den, der læses af VDMA for at undgå at rive.

Trin 4: Konfigurer Nanorouter -netværk

For at oprette et netværk ved hjælp af TPlink nanoroutere skal du tænde dem individuelt og oprette forbindelse til standard wifi SSID for enhederne. Flere oplysninger om konfigurationsindstillingerne for denne særlige enhed kan findes i enhedens brugervejledning.

Konfigurer en af enhederne som et adgangspunkt, dette fungerer som den primære forbindelse til netværket. Sørg for at navngive netværket og noter navnet, og deaktiver DHCP (vi vil ikke have, at routeren konfigurerer IP -adresserne dynamisk, vi vil have, at tansmitter og modtager Zybo -kort selv indstiller deres IP -adresser, så de er konsekvente). Efter konfigurationen skal du sørge for, at enheden genstarter og etablerer dette netværk.

Konfigurer den anden enhed som en klient, og sørg for, at den opretter forbindelse til det netværks -SSID, du konfigurerede med den første nanorouter. Sørg igen for, at DHCP er deaktiveret for klienten.

Når klienten er færdig og genstartet, skal den oprette forbindelse til adgangspunktet nanorouter (hvis den ikke gør det, er der sandsynligvis et problem i din konfiguration af en af enhederne). Du vil bemærke, at LED -lyset på klienten vil være solidt, når den har oprettet forbindelse til adgangspunktet.

Access point nanorouter LED vil sandsynligvis fortsætte med at blinke på dette tidspunkt, det er okay! Det blinkende lys betyder, at den ikke er tilsluttet en anden enhed fra dens ethernet -port, og når den er tilsluttet en konfigureret Zybo, vil LED'en forblive konstant, hvilket indikerer en vellykket netværksforbindelse.

Nu hvor vi har vores nanorouters opsætning, har vi et trådløst netværk, der giver os mulighed for at kommunikere igennem. En vigtig bemærkning er, at vores konfigurationsmetode til nanoroutere (som adgangspunkt og klient) giver os mulighed for at kommunikere fra det transmitterende Zybo -kort til det modtagende Zybo -kort, som om de to var forbundet med en enkelt ethernetledning. Dette gør vores netværksopsætning mindre vanskelig, da alternativet sandsynligvis ville indeholde konfiguration af Zybo -kortene til at oprette forbindelse til serveren eksplicit sammen med den påtænkte forbindelse.

Når begge enheder er konfigureret, er nanorouterne konfigureret og klar til at blive implementeret i dit WIDI -netværk. Der er ingen specifik sammenkobling mellem nanorouterne og Zybo -kortene, da enten adgangspunktet eller klienten fungerer for enten sende- eller modtagelsesenheden.

Trin 5: Opsætning af Zynq -behandlingssystem til dataoverførsel via Ethernet

For at overføre HDMI -dataene fra det ene Zybo -kort til det andet, skal vi indarbejde en Ethernet -protokol i vores VDMA -driver. Vores mål her er at streame individuelle videorammer via Ethernet -periferienheden i behandlingssystemet med en fastsat hastighed, der er i overensstemmelse med vores netværksbåndbredde. Til vores projekt brugte vi TCP leveret af bare metal LwIP API. Da begge projektmedlemmer er relativt uerfarne med netværksværktøjer, blev dette valg truffet uden fuldt ud at anerkende de implikationer og begrænsninger, der er forbundet med TCP. Det største problem med denne implementering var den begrænsede båndbredde og det faktum, at den virkelig ikke er designet til at dampe store datamængder. Alternative løsninger til at erstatte TCP og forbedre tbe i dette projekt vil blive diskuteret senere.

En kort beskrivelse af TCP med LwIP: Data sendes over netværket i pakker med størrelse tcp_mss (TCP maksimal segmentstørrelse), som generelt er 1460 bytes. At ringe til tcp_write vil tage nogle data, der henvises til af en markør, og konfigurere pbufs (pakkebuffere) til at gemme dataene og tilvejebringe en struktur for TCP -operationerne. Den maksimale mængde data, der kan stå i kø ad gangen, er angivet som tcp_snd_buf (TCP -afsenderbufferplads). Da denne parameter er et 16 bit -tal, er vi begrænset til en sendebufferstørrelse på 59695 bytes (der er en vis påkrævet polstring i sendebufferen). Når dataene er i kø, kaldes tcp_output for at begynde at overføre dataene. Inden du sender det næste datasegment, er det bydende nødvendigt, at alle de tidligere pakker er blevet overført. Denne proces udføres ved hjælp af funktionen recv_callback, da dette er den funktion, der kaldes, når kvitteringen ses fra modtageren.

Brug af eksempelprojekterne i Vivado SDK er meget nyttigt til at lære, hvordan LwIP TCP -operationen, og er et godt udgangspunkt for at starte et nyt projekt.

Proceduren for WiDi -sendeenheden er som følger:

- Initialiser TCP-netværket ved hjælp af bare metal-LWIP-driverfunktionsopkald.

- Angiv alle tilbagekaldsfunktioner, der er nødvendige for netværksoperationer.

- Opret forbindelse til WiDi -modtageren ved at oprette forbindelse til dens IP -adresse og port (vores konfiguration: Modtagerens IP er 192.168.0.9, forbind til port 7).

- Når VDMA -driver -timeren udløber, skal du indtaste TX ISR.

- Bestem den aktuelle rammebuffer til adgang baseret på den grå VDMA -kode

- Kør det første datasegment i kø i TCP -sendebufferen

- Output dataene, og opdater lokale variabler for at holde styr på, hvor meget data der er blevet sendt af den aktuelle ramme.

- Når du har nået det modtagne tilbagekald (funktionsopkald foretaget efter at senderen har modtaget en bekræftelse på datahentning), sætter du det næste segment af data i kø.

- Gentag trin 7 og 8, indtil hele rammen er blevet sendt.

- Vend tilbage til inaktiv tilstand for at vente på det næste timerafbrydelse for at angive, at en ny ramme er klar (Tilbage til trin 4).

Sørg for at konfigurere indstillingerne for board supportpakke LwIP som vist på billedet ovenfor. Alle værdierne er standard undtagen tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Bemærk også, at detaljeret fejlfinding kan opnås ved at ændre BSP -parametrene for gruppen debug_options.

Trin 6: Opsætning af Zynq -behandlingssystem til datamodtagelse via Ethernet

Zybo -udviklingskortet, der fungerer som den trådløse modtager, fungerer på samme måde som sendeenheden. Board support -pakkeindstillingerne for LwIP vil være identiske med dem i det foregående trin.

Enheden optager pakker, der indeholder videorammesegmenterne fra nanorouteren, og den kopierer videorammedataene til det tredobbelte rammebufferrum for den modtagende VDMA. For at undgå at overskrive data bruges en dobbelt databuffer (vi betegner netværksbufferen), når data indsamles fra nanorouteren, så netværkstrafik kan fortsætte med at streame ind, mens den foregående fulde videoramme kopieres til VDMA buffer.

Proceduren for WiDi -modtagerenheden kræver to opgaver, hvoraf den ene modtager ethernet -data, og den anden er at kopiere videorammer fra netværksbufferen til VDMA's tripel frame buffer.

Ethernet -modtagelsesopgave:

- Initialiser TCP-netværket ved hjælp af bare metal-LWIP-driverfunktionsopkald (opsætning med IP-adresse, som senderen vil oprette forbindelse til, 192.168.0.9 i vores)

- Angiv alle tilbagekaldsfunktioner, der er nødvendige for netværksoperationer.

- Efter modtaget ethernet -pakke skal du kopiere pakkedata til den aktuelle netværksbuffer, øge de nuværende akkumulerede data.

- Hvis pakken fylder netværksrammebufferen, skal du fortsætte til trin 5 og 6. Ellers skal du gå tilbage til trin 3 fra denne opgave.

- signal om, at VDMA triple frame buffer -opgaven skal kopiere fra den nyligt færdige netværksbuffer.

- Skift til den anden netværksbuffer, og fortsæt med at indsamle data via ethernet.

- Inaktiv, indtil der modtages en ny ethernet -pakke (trin 3).

Kopier netværksbuffer til VDMA triple frame buffer:

- Når VDMA -driver -timeren udløber, skal du indtaste RX ISR.

- Bestem den aktuelle rammebuffer til adgang baseret på den grå VDMA -kode.

- Bestem hvilken netværksbuffer, der skal kopieres til VDMA -bufferen, og kopier disse data

Trin 7: Tilslut dine Zybo -plader til HDMI -kilden og HDMI -vasken

Tilslut nu hdmi -kablerne til både modtageren og senderen, programmer FPGA'erne og kør behandlingssystemet. Billedhastigheden vil sandsynligvis være meget langsom på grund af den enorme overhead i LwIP -operationen og begrænset båndbredde. Hvis der er problemer, skal du oprette forbindelse via UART og prøve at identificere advarsler eller fejl.

Trin 8: Alternative ideer til forbedring

Et stort problem for dette projekt var mængden af data, der var nødvendig for at sende over wifi. Dette var forventet, men vi undervurderede den indvirkning, det ville have og resulterede i mere et burst af billeder på en skærm frem for et videofeed. Der er flere måder at forbedre dette projekt på:

- Videokomprimering i realtid. Komprimering af det indgående videofeed ramme for billede ville i høj grad reducere mængden af data, der skal sendes over netværket. Ideelt set ville dette blive gjort i hardware (hvilket ikke er en let opgave), eller det kunne gøres i software ved hjælp af den anden ARM -kerne til at køre en komprimeringsalgoritmer (dette ville have brug for yderligere analyse for at sikre, at timingen fungerer). Der er nogle open source -videokomprimeringskomponenter i realtid, vi fandt på internettet, men et flertal er IP.

- Implementering af Ethernet -strømmen i hardware frem for software. Der var masser af omkostninger på grund af manglen på plads til at stille udgående data i kø i senderen på grund af begrænsningen i segmentstørrelsen. En meget mere effektiv proces er at bruge AXI Ethernet IP med en FIFO -buffer eller DMA til at indføre data i den. Dette ville reducere den ekstra bagage fra LwIP TCP og give mulighed for mere datastrøm.

Trin 9: Tilgængelighed

Det resulterende produkt af dette WiDi -projekt skal være et fuldt integreret, kompakt par enheder, som en bruger kan tilslutte til enhver HDMI -kilde og derefter synke videofeedet til en skærm med HDMI -funktion trådløst. Enhederne ville have Zynq-7000 SoC fundet på Zybo-referencekortet og inkorporere netværkshardwaren, der findes i TP-Link nano-routere. Ideelt set ville brugeren være i stand til at styre sendemodulet fra et diskret sted inden for måloperativsystemet, med lidt behov for betydelig teknisk evne.

Sikkerhed og tilslutningsmuligheder

Enhederne skal også indeholde Transport Layer Security (TLS) og have begrænset mulighed for automatisk forbindelse, både af hensyn til privatlivets fred. Det er designernes hensigt at gøre forbindelsen til en skærm over en trådløs grænseflade til en bevidst handling på vegne af brugeren for at undgå fejlagtigt at udsende følsomt materiale.

Nuværende status

Indtil dette tidspunkt er projektets tilstand stadig meget i gang. For at den nuværende slutbruger kan drage fordel af denne vejledning, skal han eller hun have en stærk teknisk forståelse for integreret systemdesign og have en vis fortrolighed med programmerbar hardware og integreret software, der arbejder sammen.

De data, der sendes over netværket, er ikke krypteret på dette tidspunkt og formodes at være en rå transmission af TCP/IP -pakker.

Videokerneprojektet blev testet med succes for både overførsel og modtagelse. På den anden side blev den trådløse forbindelse mellem to zybo -kort etableret, og testrammedata blev sendt med succes. Det er dog stadig nødvendigt at kombinere netværkskoden til hvert videokerneprojekt og teste transmissionen af faktiske videorammer.

Anbefalede:

DIY -- Sådan laver du en edderkoprobot, der kan kontrolleres ved hjælp af smartphone ved hjælp af Arduino Uno: 6 trin

DIY || Sådan laver du en edderkoprobot, der kan styres ved hjælp af smartphone Brug af Arduino Uno: Mens du laver en edderkoprobot, kan man lære så mange ting om robotik. Ligesom at lave robotter er underholdende såvel som udfordrende. I denne video vil vi vise dig, hvordan du laver en Spider -robot, som vi kan betjene ved hjælp af vores smartphone (Androi

Kontrol ledt over hele verden ved hjælp af internet ved hjælp af Arduino: 4 trin

Kontrol ledt over hele verden ved hjælp af internet ved hjælp af Arduino: Hej, jeg er Rithik. Vi kommer til at lave en internetstyret LED ved hjælp af din telefon. Vi kommer til at bruge software som Arduino IDE og Blynk.Det er enkelt, og hvis det lykkedes dig, kan du styre så mange elektroniske komponenter, du ønskerTing We Need: Hardware:

Sådan laver du en drone ved hjælp af Arduino UNO - Lav en quadcopter ved hjælp af mikrokontroller: 8 trin (med billeder)

Sådan laver du en drone ved hjælp af Arduino UNO | Lav en Quadcopter ved hjælp af mikrokontroller: Introduktion Besøg min Youtube -kanal En Drone er en meget dyr gadget (produkt) at købe. I dette indlæg vil jeg diskutere, hvordan jeg gør det billigt ?? Og hvordan kan du lave din egen sådan til en billig pris … Nå i Indien alle materialer (motorer, ESC'er

RF 433MHZ radiostyring ved hjælp af HT12D HT12E - Lav en RF -fjernbetjening ved hjælp af HT12E & HT12D med 433mhz: 5 trin

RF 433MHZ radiostyring ved hjælp af HT12D HT12E | Oprettelse af en RF -fjernbetjening ved hjælp af HT12E & HT12D med 433mhz: I denne instruktør vil jeg vise dig, hvordan du laver en RADIO -fjernbetjening ved hjælp af 433mhz sendermodtagermodul med HT12E -kode & HT12D -dekoder IC.I denne instruktive kan du sende og modtage data ved hjælp af meget meget billige KOMPONENTER SOM: HT

Quadcopter Brug af Zybo Zynq-7000 Board: 5 trin

Quadcopter Brug af Zybo Zynq-7000 Board: Inden vi går i gang, er her nogle ting, du vil have til projektet: Deleliste1x Digilent Zybo Zynq-7000 board 1x Quadcopter Frame i stand til at montere Zybo (Adobe Illustrator-fil til laserskæring vedhæftet) 4x Turnigy D3530/ 14 1100KV børsteløse motorer 4x