Indholdsfortegnelse:

- Trin 1: Konfiguration af Vivado

- Trin 2: Emballage VGA Driver IP

- Trin 3: Zynq IP

- Trin 4: GPIO IP

- Trin 5: Bloker hukommelse

- Trin 6: Anden IP

- Trin 7: SDK

- Trin 8: Konklusion

Video: Spejlvisning: 8 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:28

Målet med dette projekt er at skabe billedvisningens funktionalitet for et Smart Mirror. Spejlet kan vise prognoser (solrig, delvis solrig, overskyet, blæsende, regn, torden og sne) og temperaturværdier fra -9999 ° til 9999 °. Prognoser og temperaturværdier er hårdt kodet, som om de skal efterlignes ved at blive analyseret fra et vejr -API.

Projektet bruger et Zynq-Zybo-7000-kort, der kører FreeRTOS og bruger Vivado 2018.2 til at designe og programmere hardwaren.

Dele:

Zynq-Zybo-7000 (med FreeRTOS)

19 LCD (640x480)

VGA -kabel

12 "x 18" akryl spejl

Trin 1: Konfiguration af Vivado

Download Vivado 2018.2 fra Xilinx, og brug Webpack -licensen. Start Vivado og "Opret nyt projekt", og giv det et navn. Vælg derefter "RTL -projekt", og markér "Angiv ikke kilder på nuværende tidspunkt." Når du vælger en del, skal du vælge "xc7z010clg400-1" og hit "Afslut" på den næste side.

Trin 2: Emballage VGA Driver IP

Føj filen vga_driver.sv til designkilderne. Klik derefter på "Værktøjer" og vælg "Opret og pakk ny IP". Vælg "Pak dit nuværende projekt". Vælg derefter en IP -placering og "Inkluder.xci -filer." Klik på "OK" i pop op -vinduet og derefter på "Afslut".

Gå til "Emballagetrin" til "Gennemgang og pakke", og vælg "Pakke -IP".

Nu skulle vga_driver være tilgængelig som en IP -blok.

Trin 3: Zynq IP

Vælg "Opret blokdesign" under afsnittet "IP Integrator". Tilføj "ZYNQ7 Processing System", og dobbeltklik på blokken. Klik på "Importer XPS -indstillinger", og upload filen ZYBO_zynq_def.xml.

Dernæst skal du under "PS-PL-konfiguration" åbne rullemenuen for "AXI Non Secure Enablement" og kontrollere "M AXI GP0 interface."

Dernæst skal du under "MIO -konfiguration" åbne rullemenuen for "Application Processor Unit" og kontrollere "Timer 0" og "Watchdog".

Endelig skal du under "Urkonfiguration" åbne rullemenuen for "PL Fabric Clocks" og kontrollere "FCLK_CLK0" og ved 100 MHz.

Trin 4: GPIO IP

Tilføj to GPIO -blokke til blokdesignet. GPIO'erne bruges til at styre pixeladressen og pixelernes RGB -komponenter. Konfigurer blokkene som vist på billederne ovenfor. Når du har tilføjet og konfigureret begge blokke, skal du klikke på "Kør forbindelsesautomatisering".

GPIO 0 - Kanal 1 styrer pixeladressen, og kanal 2 styrer den røde farve.

GPIO 1 - Kanal 1 styrer den grønne farve, og kanal 2 styrer den blå farve.

Trin 5: Bloker hukommelse

Tilføj en blokhukommelsesgenerator -IP til blokdesignet, og konfigurer som vist ovenfor. Pixelfarverne skrives til hukommelsesadresser, som derefter læses af VGA -driveren. Adresselinjen skal matche mængden af pixels, der bruges, så den skal være 16 bit. Dataene i er også 16 bits, da der er 16 farvebits. Vi er ligeglade med at læse nogen anerkendelsesbits.

Trin 6: Anden IP

Den vedhæftede pdf viser det færdige blokdesign. Tilføj den manglende IP, og afslut forbindelserne. Også "Make Externals" til VGA -farveudgange og de lodrette og vandrette synkroniseringsudgange.

xlconcat_0 - Sammenkæder de enkelte farver for at danne et 16 bit RGB -signal, der føres ind i Block RAM.

xlconcat_1 - Sammenkæder kolonne- og ræksignalerne fra VGA -driveren og føres ind i Port B i Block RAM. Dette gør det muligt for VGA -driveren at læse pixelfarveværdier.

VDD - Konstant HIGH forbundet til skrive -aktiveringen af Block RAM, så vi altid kan rette det.

xlslice_0, 1, 2 - Skiverne bruges til at bryde RGB -signalet til individuelle R-, G- og B -signaler, der kan indføres i VGA -driveren.

Når blokdesignet er fuldført, skal du generere en HDL -indpakning og tilføje begrænsningsfilen.

*Blokdesign er baseret på selvstudiet skrevet af benlin1994*

Trin 7: SDK

Koden, der kører dette blokdesign, er inkluderet nedenfor. Init.c indeholder de funktioner, der håndterer tegningen (prognoser, tal, gradersymbol osv.). Hovedløkken i main.c er det, der bliver kørt, når tavlen er programmeret. Denne loop indstiller prognose- og temperaturværdierne og kalder derefter draw -funktionerne i init.c. Den går i øjeblikket igennem alle syv prognoser og viser den ene efter den anden. Det anbefales, at du tilføjer et brudpunkt på linje 239, så du kan se hvert billede. Koden kommenteres og giver dig mere information.

Trin 8: Konklusion

For at forbedre det nuværende projekt kunne man uploade forudindlæste prognosebilleder i form af COE -filer til Block Memory Generators. Så i stedet for at tegne prognoserne manuelt som vi gjorde i C -koden, kunne man få billederne læst ind. Vi forsøgte at gøre dette, men kunne ikke få det til at fungere. Vi var i stand til at læse pixelværdier og udsende dem, men det skabte rodede billeder, der ikke lignede dem, vi uploadede til RAM. Block Memory Generator -databladet er nyttigt at læse.

Projektet er i det væsentlige et halvt Smart Mirror, da det mangler internetforbindelsesaspektet. Tilføjelse af dette ville give et komplet Smart Mirror.

Anbefalede:

Arduino bil omvendt parkering alarmsystem - Trin for trin: 4 trin

Arduino bil omvendt parkering alarmsystem. Trin for trin: I dette projekt vil jeg designe en simpel Arduino bil omvendt parkeringssensorkreds ved hjælp af Arduino UNO og HC-SR04 ultralydssensor. Dette Arduino -baserede bilomvendt alarmsystem kan bruges til en autonom navigation, robotafstand og andre rækkevidde

Trin for trin pc -bygning: 9 trin

Trin for trin PC Building: Supplies: Hardware: MotherboardCPU & CPU -køler PSU (strømforsyningsenhed) Opbevaring (HDD/SSD) RAMGPU (ikke påkrævet) CaseTools: Skruetrækker ESD -armbånd/mathermal pasta m/applikator

Tre højttalerkredsløb -- Trin-for-trin vejledning: 3 trin

Tre højttalerkredsløb || Trin-for-trin vejledning: Højttalerkredsløb styrker lydsignalerne, der modtages fra miljøet til MIC og sender det til højttaleren, hvorfra forstærket lyd produceres. Her vil jeg vise dig tre forskellige måder at lave dette højttalerkredsløb på:

Trin-for-trin uddannelse i robotik med et sæt: 6 trin

Trin-for-trin uddannelse i robotteknologi med et kit: Efter ganske få måneder med at bygge min egen robot (se alle disse), og efter at jeg to gange havde dele mislykkedes, besluttede jeg at tage et skridt tilbage og tænke min strategi og retning. De flere måneders erfaring var til tider meget givende, og

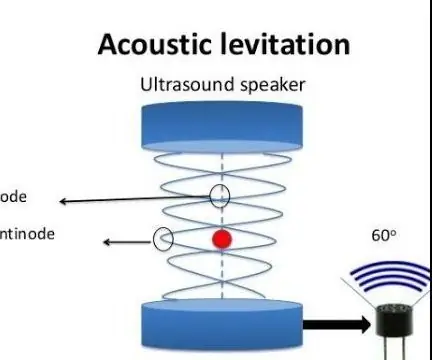

Akustisk levitation med Arduino Uno trin for trin (8 trin): 8 trin

Akustisk levitation med Arduino Uno Step-by Step (8-trin): ultralyds lydtransducere L298N Dc kvindelig adapter strømforsyning med en han-DC-pin Arduino UNOBreadboard Sådan fungerer det: Først uploader du kode til Arduino Uno (det er en mikrokontroller udstyret med digital og analoge porte til konvertering af kode (C ++)