Indholdsfortegnelse:

- Trin 1: Opbygning af et PWM-modul- kildefil

- Trin 2: Opbygning af et PWM-modul- Vivado Setup

- Trin 3: Opbygning af et PWM-modul- Opret en projektfil

- Trin 4: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (I)

- Trin 5: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (II)

- Trin 6: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (III)

- Trin 7: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (IV)

- Trin 8: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (V)

- Trin 9: Opbygning af et PWM-modul- Hardwareinstallation

- Trin 10: Opbygning af et PWM-modul- Generer Bitstream og start SDK

- Trin 11: Opbygning af et PWM-modul- Opret en ny applikation i Xilinx SDK

- Trin 12: Opbygning af et PWM-modul- Oversigt over Project Explorer (I)

- Trin 13: Opbygning af et PWM-modul- Oversigt over Project Explorer (II)

- Trin 14: Opbygning af et PWM-modul- Oversigt over Project Explorer (III)

- Trin 15: Opbygning af et PWM-modul- Afslutning af PWM-funktion (I)

- Trin 16: Opbygning af et PWM-modul- Afslutning af PWM-funktion (II)

- Trin 17: Opbygning af et PWM-modul- Afslutning af PWM-funktion (III)

- Trin 18: Opbygning af et PWM-modul- Få det til at køre

- Trin 19: Streaming af videobehandling på Digilent ZYBO med OV7670

- Trin 20: Komplet blokdiagram

- Trin 21: Tilslut OV7670 til ZYBO

- Trin 22: Opret blokdesign

- Trin 23: Tilføj VHDL -filer til OV7670 kamerakontrol og optagelse

- Trin 24: Tilføj begrænsningsfil

- Trin 25: Tilføj IP Repo for HLS IP

- Trin 26: Tilføj moduler og IP

- Trin 27: IP -konfigurationsindstillinger

- Trin 28: Tilføj og konfigurer PS IP -blok

- Trin 29: Del 1. Opbygning af et PWM -modul til servomotorer

- Trin 30: Videoinput sideforbindelser (aclk fremhævet)

- Trin 31: Tilslutninger til OV7670

- Trin 32: Tilslutninger på Video Out Side

- Trin 33: Kør Block and Connection Automation

- Trin 34: Generer HDL Wrapper

- Trin 35: Generer Bitstream, eksporter hardware til SDK, start SDK fra Vivado

- Trin 36: SDK (ingen FreeRTOS)

- Trin 37: FreeRTOS -implementering

- Trin 38: Brugsanvisning

- Trin 39: Referencer og links

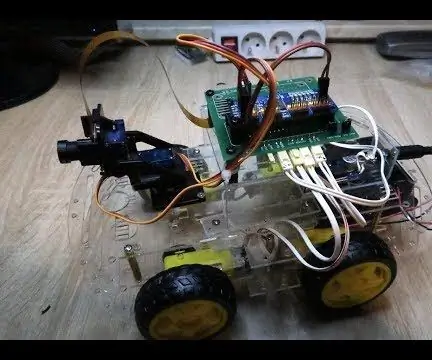

Video: ZYBO OV7670 kamera med panorering/vippekontrol: 39 trin (med billeder)

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:29

Start med trin et for detaljer om bare at oprette en 2-akset servo PWM-controller.

Start med det massive blokdiagram (trin 19) for hele projektet.

Kamera + Pan/tilt -opsætning, vi brugte:

PmodCON3 fra Digilent blev brugt til at forbinde servoer.

Trin 1: Opbygning af et PWM-modul- kildefil

Trin 2: Opbygning af et PWM-modul- Vivado Setup

Download først Vivado Design Suite From Xilinx -webstedet. Installer hele designsuiten, herunder Vivado Software Development Kit (SDK). Dette projekt bruger version 2017.2.

I mellemtiden skal Digilent Adept 2 også installeres som en Zybo -kortdriver.

Trin 3: Opbygning af et PWM-modul- Opret en projektfil

Inden du opretter en projektfil, skal du sikre dig, at du allerede har installeret Zybo -filen korrekt som vejledning her:

Vivado version 2015.1 og senere boardfilinstallation

Åbn Vivado 2017.2. I hurtig start skal du klikke på Opret projekt -> Næste -> Projektnavn (Navngiv dit projektnavn her) -> Projekttype. På projekttype skal du vælge RTL Project og markere "Angiv ikke kilder på nuværende tidspunkt". Vælg derefter "Standards" og "Zybo" som standardnavn for standarddelen. Klik derefter på Udfør for at starte projektet.

Trin 4: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (I)

Klik på “” Opret blokdesign”i Flow Navigator, og tryk derefter på OK. klik på "+" -tegnet for at tilføje nødvendige IP'er. Tilføje:

- Et ZYNQ7 -behandlingssystem To AXI -timer

- To AXI -timer

Trin 5: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (II)

Efter tilføjelse af IP'er skal du køre Block Automation og forbindelsesautomatisering. Når automatiseringen er fuldført, skal du på blokken “axi_timer_0” højreklikke på pwm0 -> Lav ekstern. Navngiv pwm0 ekstern pin som pwm_Xaxis. Gentag også ovenstående proces på blokken "axi_timer_1" og navngiv pwm0 ekstern pin som pwm_Zaxis.

Trin 6: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (III)

Bemærk, at hver gang vi afslutter Block Design i Vivado, skal vi oprette en HDL Wrapper. Da det vil være modulet på topniveau for hvert projekt.

Trin 7: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (IV)

Nu skal vi oprette vores begrænsningsfil for at tildele stifter, der er forbundet til vores blokdiagram. Luk vinduet Blokdesign, på fanen Kilder, "Tilføj kilder"-> Tilføj eller opret begrænsninger-> tilføj Zybo-Master.xdc som vores begrænsningsfiler.

Trin 8: Opbygning af et PWM-modul- Blokdesign og begrænsningsfilindstilling (V)

Åbn begrænsningsfilen Zybo-Master.xdc fra mappen Begrænsninger, fjern en kommentar til de porte, vi vil angive som udgangssignaler, og omdøb "get_ports {XXXX}", som XXXX angiver den eksterne pin, der er navngivet i blokdiagrammet. Indstillingen af begrænsningsfil vises på figuren.

Trin 9: Opbygning af et PWM-modul- Hardwareinstallation

Tilslut servomotorer til Pmod CON3. TowerPro SG90 er den servomotormodel, vi brugte i dette projekt. For servomotortråde repræsenterer den orange ledning PWM -signalet, der er forbundet til SIG -pin i Pmod CON3. Den røde ledning Vcc er en strømledning forbundet til VS pin i Pmod CON3. Endelig er den brune ledning Gnd en jordledning, der er forbundet med GND -stiften. Indsæt derefter Pmod CON3 til den øverste række af JD -port i Zybo -kortet.

Trin 10: Opbygning af et PWM-modul- Generer Bitstream og start SDK

1. Kør Generer BitStream på fanen Project Navigator.

2. Export hardware: File> Export> Export Hardware-> mark on "include bitstream"-> OK 3. Launch SDK: File-> Launch SDK.

Trin 11: Opbygning af et PWM-modul- Opret en ny applikation i Xilinx SDK

Opret en ny applikation:

Fil> Ny> Applikationsprojekt -> Indtast navnet på dit projekt -> Afslut

Under Project Explorer skal der være tre mapper.

I dette tilfælde er “design_1_wrapper_hw_platform_0” den mappe, der tidligere blev eksporteret af Vivado. Axis_2_PWM_SDK_bsp er mappens supportpakke. Og Axis_2_PWM_SDK er vores hovedprojektmappe i SDK. Du kan se filen "helloworld.c" under mappen "src" i Axis_2_PWM_SDK, hvor "helloworld.c" er hovedfilen.

Trin 12: Opbygning af et PWM-modul- Oversigt over Project Explorer (I)

Lad os kontrollere nogle filer under Project Explorer. Åbn først "system.hdf" i mappen "design_1_wrapper_hw_platform_0". Denne fil viser adressekortet til processor ps7_cortex9 og de IP -blokke, der findes i vores design.

Trin 13: Opbygning af et PWM-modul- Oversigt over Project Explorer (II)

Kontroller derefter filen "inkluder" og "libsrc" under mappen "Axis_2_PWM_SDK_bsp". Biblioteksfiler her gør det muligt for os at interagere med hardwareudstyr uden at "afspille" registre.

Trin 14: Opbygning af et PWM-modul- Oversigt over Project Explorer (III)

Gennem BSP -dokumentationen findes xtmrctr.h som et Xilinx Timer Control Library relateret til AXI Timer. Typisk kunne vi finde den ønskede PWM -funktion her. Men hvis du læser dokumentationen "tmrctr_v4_3", viser det, at driveren i øjeblikket ikke understøtter PWM -driften af enheden. På grund af manglen på PWM -funktion skal vi afslutte vores PWM -funktion ved hjælp af xtmrctr.h og AXI Timer v2.0 LogiCORE IP -produktguide.

Trin 15: Opbygning af et PWM-modul- Afslutning af PWM-funktion (I)

Tilbage til hovedfilen "helloworld.c" inkluderer følgende overskriftsfiler:

Trin 16: Opbygning af et PWM-modul- Afslutning af PWM-funktion (II)

Definer basisadresserne for to AXI TImer gennem “xparameters.h”.

Trin 17: Opbygning af et PWM-modul- Afslutning af PWM-funktion (III)

Byg den ønskede PWM -funktion.

Duty_val: konverterer gradværdien til duty cycle. PWM_Freq_Duty: indstil den ønskede frekvens og driftscyklus for at generere PWM. Urperiode bør også tildeles.

PWM_START: tildel PWM -registeradressen, og begynd at generere PWM.

PWM_STOP: tildel PWM -registeradressen, og stop med at generere PWM.

Resten af demokoden vises i “helloworld.c” under “Axis_2_PWM_SDK”

Trin 18: Opbygning af et PWM-modul- Få det til at køre

1. Programmer FPGA'en gennem SDK

- Tilslut Zybo Board via USB -port til pc.

- Xilinx Tools -> Program FPGA

2. Kør programmet

Klik på ikonet "Kør", og slip menuen -> Kør som -> Start på hardware

3. SDK Terminal

- Åbn SDK -terminalen -> Opret forbindelse til seriel port -> OK

- Kør programmet. Hvis demokoden kører med succes, skal du se "Initialisering udført!" på SDK -terminalen.

Trin 19: Streaming af videobehandling på Digilent ZYBO med OV7670

Komplet arkivfil vedhæftet.

Trin 20: Komplet blokdiagram

Dette viser det komplette diagram over alle forbindelser og IP -blokke i projektet

Trin 21: Tilslut OV7670 til ZYBO

Opret en forbindelse til at koble ov7670 -modulet til ZYBO Pmods

Data Pmod er Pmod D

Kontrol Pmod er Pmod C

Tilslut desuden PmodCON3 og servoer som specificeret i første halvdel af denne vejledning

Trin 22: Opret blokdesign

I Flow Navigator skal du klikke på "Opret blokdesign", og tryk derefter på OK.

Trin 23: Tilføj VHDL -filer til OV7670 kamerakontrol og optagelse

Tilføj de VHDL -filer, der er knyttet til dette trin, til projektet

Trin 24: Tilføj begrænsningsfil

Tilføj den vedhæftede begrænsningsfil til dit projekt.

Trin 25: Tilføj IP Repo for HLS IP

Tag den vedhæftede Zip -fil, og pak den ud i en ny mappe med samme navn i en ny mappe (mappe) kaldet "HLS_repo".

Føj et IP-lager til dit projekt ved at gå til IP-kataloget og højreklik på "Tilføj depot …"

Naviger til dit "HLS_repo" bibliotek, og vælg det.

Valgfrit: Opret HLS -videobearbejdningsblokken til dig selv!

Trin 26: Tilføj moduler og IP

Føj modulerne ov7670_axi_stream_capture, debounce og ov7670_controller til blokdiagrammet ved at højreklikke på baggrunden og vælge "Tilføj modul …"

Tilføj på samme måde IP'erne:

- HLS_Video_Track

- Videoramme buffer buffer

- Videoramme Buffer læst

- Video Timing controller

- AXI4-Stream til videoudgang

- 3 af "Skive"

- Konstant

- 2 af AXI Timer

Trin 27: IP -konfigurationsindstillinger

Som vist på billederne

Trin 28: Tilføj og konfigurer PS IP -blok

Tilføj ZYNQ7 Processing System til blokdiagrammet

rediger konfigurationen:

-

PS-PL-konfiguration

-

HP

- Aktiver S HP 0

- Aktiver S HP 1

-

-

Urkonfiguration

-

PL stofure

- FCLK_0 ved 100MHz

- FCLK_1 ved 25MHz (OutputClock)

- FLCK_2 ved 35MHz (<= 50MHz) (CameraClock)

-

Trin 29: Del 1. Opbygning af et PWM -modul til servomotorer

Hent axi_timer_0 pwm0 til den nye outputport pwm_Xaxis

Hent axi_timer_1 pwm0 til den nye outputport pwm_Zaxis

Trin 30: Videoinput sideforbindelser (aclk fremhævet)

Tilslut videoindgangssidens IP -blokke korrekt

(* disse forbindelser skal oprettes ved at vælge de rigtige muligheder under forbindelsesautomatisering) "aclk" fra axi_stream_capture går til:

- ap_clk på videoramme buffer skrive

- ap_clk på HLS videostream -behandlingsblok

- *aclk på AXI smartconnect IP fra Video Frame Buffer Skriv til S_AXI_HP0

- *aclk svarende til kanalerne i AXI Interconnect IP for S_AXI -kanalerne i HLS -videobehandlingsblokken og videoramebufferen, skriver S_AXI_HP0_ACLK på PS -blokken

Videostreamsignalet er simpelthen forbundet i serie fra fangstblokken til Zynq -hukommelsesgrænsefladen.

- Video går fra optagelsesblok til HLS -behandlingsblok.

- Den behandlede video fra HLS -blokken går til rammebuffer -skriveblokken.

- *Rammebuffer -skriveblokken opretter forbindelse til HP0 -grænsefladen på Zynq PS -blokken.

- M_axis_tuser -signalet fra output fra capture blokken ledes manuelt til både video_in_TUSER input signalet på HLS behandlingsblokken og ap_start signalet på den samme blok.

TUSER (tuser) -signalet bruges af AXI -videostrømprotokollen til at angive starten på en ramme i videoen. AP_Start fortæller HLS -blokken at starte behandlingen. Vi bruger således tuser til at aktivere HLS -blokken til at behandle hvert billede, som det kommer ind. Når man tilslutter et enkelt signal fra en bus og opdeler det på denne måde, er det nødvendigt også at tilslutte det normale afslutningspunkt for resten af bussen. Vivado antager, at hvis du tilslutter signalet manuelt, at du vil afbryde, hvad det normalt ville forbinde til.

Konfigurationsindstillinger for IP -blokke:

Videoramme buffer skriver:

Videoformater: RGB8

1 prøve pr. Ur Maks. Kolonner: 1280 (> = 640) Maks. Rækker: 960 (> = 480) Maks. Databredde: 8

Trin 31: Tilslutninger til OV7670

På ov7670_axi_stream_capture -blokken

- Gør alle input eksterne (højreklik på en nål og vælg fra menuen, eller klik med venstre-> ctrl+T)

- Lad navnene være som de er

På ov7670_controller blokken

- Gør alle blokudgange eksterne

- Omdøb den config_finished port til led0

- tilslut clk til CameraClock (<= 50MHz) (FCLK_2)

På debounce -blokken

- tilslut knappen 1 til en ekstern indgangsport kaldet btn0

- tilslut out1 til genudsendelseslinjen på ov7670_controller IP -blokken

- tilslut knappen 2 til en ekstern indgangsport kaldet btn3

- tilslut out2n til ext_reset_in -input på processorsystemets nulstillings -IP for videooptagelsesurets domæne. (*Dette skal muligvis gøres, efter at IP er genereret*)

- tilslut clk til CameraClock (<= 50MHz) (FCLK_2)

Trin 32: Tilslutninger på Video Out Side

Forbindelser til blokke Video Timing Controller (VTC), AXI4-Stream til Video Out og skiver

- Brug 25MHz ur (FCLK_1) til vid_io_out_clk og VTC clk

- Brug 100MHz ur (FCLK_0) til aclk på AXI4-Stream til Video Out

- vtiming_out til vtiming_in

- Video Frame Buffer Læs m_axis_video går til AXI4-Stream til Video Out video_in

- vtg_ce går til gen_clken

- Bind VTC clken, aclken, vid_io_out_ce til Constant dout [0: 0]

- Bring vid_hsync og vid_vsync ud til henholdsvis eksterne outputporte vga_hs og vga_vs. (ikke på billedet)

Skiver:

-

Skiver skal opsættes som vist på vedhæftede billeder

- omdøb blokkene til slice_red, slice_green og slice_blue

- opsætningsskiveområder som vist på billederne pr. navn på blokken

- tilslut hver skiveudgang til en ekstern portudgang som vist på billedet.

- vid_data [23: 0] opretter forbindelse til input for hvert stykke (Din [23: 0])

Trin 33: Kør Block and Connection Automation

Kør Block Automation for at forbinde tingene fra ZYNQ7 PS -blokken. Som vist på billedet.

Kør forbindelsesautomatisering for at oprette alle sammenkoblede IP. Vær meget opmærksom på alle muligheder i hvert billede.

På debounce -blokken skal du forbinde out2n til videooptagelsesurets domæne Processor System Reset ext_reset_in input.

Trin 34: Generer HDL Wrapper

Generer HDL Wrapper til dit blokdesign.

Indstil det som det øverste modul.

Trin 35: Generer Bitstream, eksporter hardware til SDK, start SDK fra Vivado

Sørg for at inkludere bitstream i eksporten.

Generering af bitstream kan tage meget lang tid.

Start derefter SDK

Trin 36: SDK (ingen FreeRTOS)

Denne version gør alt uden at bruge FreeRTOS, og kondenserer koden pænt.

Opret en selvstændig BSP baseret på hardware design. Standardindstillingerne skal være fine. Sørg for, at BSP -kilder er blevet genereret.

Opret app som vist på billedet. (tom ansøgning)

Slet den autogenererede hovedfil, og importer de vedhæftede filer.

Trin 37: FreeRTOS -implementering

Denne version bruger FreeRTOS. Opret en FreeRTOS901 BSP baseret på hardwaredesignet. Standardindstillingerne skal være fine. Sørg for, at BSP -kilder er blevet genereret.

Opret app som vist på billedet. (tom ansøgning)

Slet den autogenererede hovedfil, og importer de vedhæftede filer.

Trin 38: Brugsanvisning

Dette projekt er lidt svært at komme i gang. Følg trinene i rækkefølge.

Sørg for, at din ZYBO ikke selvlader noget, når den tændes. Det betyder, at Done LED ikke skal lyse. En måde at gøre dette på er at indstille startkildespringeren til JTAG.

Åbn det projekt (FreeRTOS eller ej), du vil programmere fra SDK

- Tænd din ZYBO. Done LED skal ikke lyse.

- Programmer FPGA'en med bitfilen. Done LED skal lyse. Led0 skal ikke lyse.

- Kør koden (husk at gå forbi startbrudpunktet, hvis du gør det).

På dette tidspunkt skal du få output på din VGA -skærm.

For at genstarte (hvis det er fejl eller hvad som helst): tryk hurtigt på PS-SRST-knappen, eller sluk for ZYBO og derefter igen. Fortsæt fra trin 2.

Hvis du standser processoren med fejlfinding, får kameraet til at holde position i stedet for at bevæge sig. Videostrømmen fortsætter alligevel.

Trin 39: Referencer og links

Xilinx referencevejledninger og dokumentation:

- PG044 - AXI -Stream til videoudgang

- PG278 - Videoramme buffer læser/skriver

Andre links:

- Lauris blog - VDMA -input

- Lauris blog - OV7670 til VGA -output ved hjælp af BRAM

- Hamsterworks wiki, af Mike Fields, den originale kilde til OV7670 -koden

- Datablad med grundlæggende timingspecifikationer

Anbefalede:

Sådan adskilles en computer med nemme trin og billeder: 13 trin (med billeder)

Sådan adskilles en computer med nemme trin og billeder: Dette er en instruktion om, hvordan du adskiller en pc. De fleste af de grundlæggende komponenter er modulopbyggede og nemme at fjerne. Det er dog vigtigt, at du er organiseret omkring det. Dette hjælper med at forhindre dig i at miste dele og også ved at lave genmonteringen til

WIDI - Trådløs HDMI ved hjælp af Zybo (Zynq Development Board): 9 trin (med billeder)

WIDI - Trådløs HDMI ved hjælp af Zybo (Zynq Development Board): Har du nogensinde ønsket, at du kunne slutte dit tv til en pc eller bærbar som en ekstern skærm, men ønskede ikke at have alle de irriterende ledninger i vejen? I så fald er denne tutorial lige noget for dig! Selvom der er nogle produkter ude, der opnår dette mål, er en

RasbperryPi bil med FPV kamera. Kontrol med webbrowser: 31 trin (med billeder)

RasbperryPi bil med FPV kamera. Kontrol med webbrowser: Vi bygger en 4 -hjulet bil - styretøjet ligner en tank - for at dreje den ene side af hjulene vil rotere med anden hastighed end den anden. Ved bilen placeres kameraet på en særlig holder, hvor vi kan ændre kameraposition. Robotten bliver c

Laser Harp Synthesizer på Zybo Board: 10 trin (med billeder)

Laser Harp Synthesizer på Zybo Board: I denne vejledning opretter vi en fuldt funktionel laserharpe ved hjælp af IR -sensorer med et serielt interface, der gør det muligt for brugeren at ændre tuning og tone på instrumentet. Denne harpe bliver det 21. århundredes nyindspilning af det ældgamle instrument. Det

Kamera til Time Lapse -billeder, der er lette: 22 trin (med billeder)

Kamera til Time Lapse -billeder på en let måde: Jeg tjekkede en af de andre instruktioner om at lave time -lapse -film. Han dækkede ganske godt filmdelen. Han fortalte om den gratis software, som du kunne downloade for at lave filmene. Jeg sagde til mig selv, jeg tror, at jeg vil se, om jeg kan