Indholdsfortegnelse:

- Trin 1: Brugerbetjening af Digital Sequencer

- Trin 2: Tekniske detaljer

- Trin 3: Tekniske detaljer

- Trin 4: 7-segment Clock Divider

- Trin 5: Beats Per Minute Clock Divider

- Trin 6: Pitches Clock Divider

- Trin 7: Afspil/Pause/Vælg statsmaskine

- Trin 8: Afspil/Pause/Vælg tilstandsmaskine

- Trin 9: Output FSM

- Trin 10: Output FSM

- Trin 11: Bemærk Tildel

- Trin 12: Vælg output

- Trin 13: Square Wave Gen

- Trin 14: 7-segment display

- Trin 15: Endeligt valg

- Trin 16: Eksterne enheder: DAC

- Trin 17: Eksterne enheder: Højttaler

- Trin 18: Videodemo

- Trin 19: VHDL -kode

Video: 4 -trins digital sekvens: 19 trin (med billeder)

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:29

CPE 133, Cal Poly San Luis Obispo

Projektskabere: Jayson Johnston og Björn Nelson

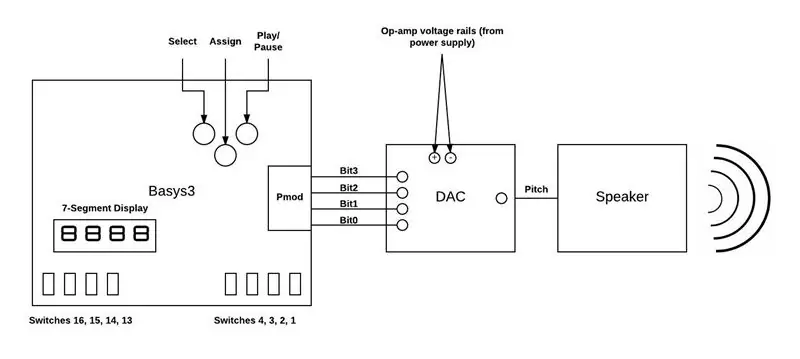

I nutidens musikindustri er et af de mest almindeligt anvendte "instrumenter" den digitale synthesizer. Hver musikgenre, fra hip-hop til pop og endda country, bruger en digital synthesizer i studiet til at skabe de beats og lyde, de har brug for for at bringe deres musik til live. I denne vejledning opretter vi en meget enkel synthesizer med Basys 3 FPGA -kortet.

Synthesizeren vil kunne spille fire udvalgte kvartnoter med et konstant antal slag i minuttet. Brugere vil bruge switchene til at tildele hver kvartnote til en musikalsk tonehøjde. Til dette projekt bruger vi en 4-bit digital til analog converter (DAC) til at tage output fra kortet og konvertere det til et analogt signal. Outputtet fra DAC'en vil derefter blive ført til en standard computerhøjttaler, hvilket skaber vores musik. Seksten diskrete pladser er mulige. Vi vil begrænse vores synthesizer til en enkelt oktav på 12 toner, der ligger mellem midten C (261,6 Hz) og B4 (493,9 Hz). Brugeren har også mulighed for at tildele flere noter på samme tid, samt tildele en pause ved at trykke på tildele, mens ingen af pitchkontakterne er forskudt opad. Efterhånden som hver note vælges og afspilles, vises bogstavnoten på 7-segment displayet. Vi vil også bruge tre af knapperne på tavlen, en til afspilning og pause af musikken, en til at nulstille synthesizeren og sætte den i "markering" -tilstand, og den tredje til at tildele hver note en tonehøjde, mens den er i valgtilstand.

Når brugeren er tilfreds med sit valg af noter, og efter at have trykket på afspilningsknappen, vil synthesizeren afspille hver note gentagne gange, indtil brugeren enten trykker på pause eller vælger.

Her er en liste over det nødvendige udstyr:

- Vivado (eller ethvert VHDL -arbejdsområde)

- Basys 3 eller lignende FPGA board

- Digital til analog omformer (min. 4-bit)

- Højttaler med hovedtelefonstik

- Wire fører

Trin 1: Brugerbetjening af Digital Sequencer

Følgende trin er at betjene den digitale sequencer. Den digitale sequencer understøtter afspilning af 12 forskellige tonehøjder (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), der spænder fra 261,6 Hz til 493,9 Hz.

1. Tryk på den venstre knap for at sætte tavlen i valgtilstand. I denne tilstand bruges de fire switches til venstre (switch 13 til 16) hver til at gemme en tydelig pitch -værdi.

2. For at foretage et valg skal du tænde en af de venstre kontakter og derefter bruge de 4 kontakter til højre (switch 1 til 4) til at vælge en ønsket tonehøjde. Pitchen, der er knyttet til en bestemt kombination af højre switches, vises på syv segmentdisplayet, og displayet opdateres til den nye associerede pitch, når de rigtige switches flyttes til en ny kombination. En hvil kan tildeles ved aldrig at tildele en tonehøjde til en af de venstre kontakter eller ved at tildele en tonehøjde vist som 0 på displayet til sedlen. Når den ønskede tonehøjde er fundet og vises på displayet, skal du trykke på den nederste tildelingsknap for at tildele den specifikke tonehøjde til noten.

3. Gentag trin 2 for de tre resterende toner ved at vende hver af de resterende venstre switches individuelt, vælge den respektive tonehøjde med de højre switches og trykke på den nederste knap for at tildele tonehøjden til noten. Flere noter kan tildeles den samme tonehøjde ved at flytte mere end en af de venstre kontakter opad på samme tid.

4. Nu hvor alle tonepladserne er tildelt, er den digitale sequencer klar til at spille. For at afspille noterne på højttaleren skal du blot trykke på den højre afspilning/pause -knap for at begynde at afspille musikken. Rækkefølgen for afspilningssekvensen afspejler tonehøjderne, der er forbundet med de venstre kontakter, fra venstre mod højre. Noterne vil blive spillet med et bestemt antal slag i minuttet, i rækkefølgen 1, 2, 3, 4, 1, 2…. Displayet viser den note, der aktuelt afspilles, mens højttalerne afspiller musikken. For at sætte musikafspilningen på pause, skal du blot trykke på den højre knap, og derefter stopper musikken med at afspille, og der vises et pausesymbol på displayet. Tryk på den højre knap igen for at genoptage afspilningen.

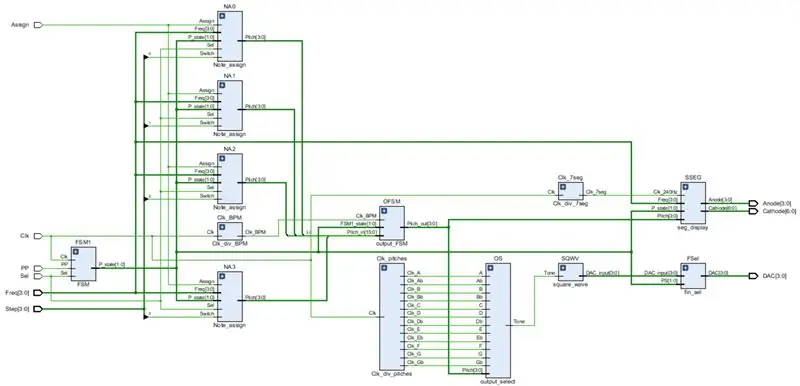

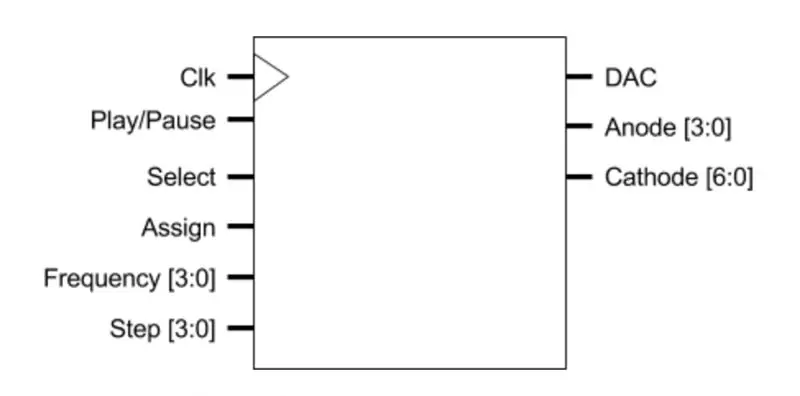

Trin 2: Tekniske detaljer

Vores synthesizer gør brug af mange forskellige digitale komponenter. Inkluderet er endelige tilstandsmaskiner, registre, multiplexere, urdelere og mere. Til at bygge vores synthesizer brugte vi 10 unikke modulære filer. I stedet for at gøre hvert modul til en komponent, brød vi de modulære filer ned efter funktion. De fleste moduler er derfor mere end en komponent. Bemærk billedet ovenfor viser hver blok, der er bundet sammen i vores topdesign.

Vi vil diskutere hvert modul ved at beskrive input og output, nedbryde dets komponenter og forklare dets formål i det overordnede design. En ZIP -fil er inkluderet i bunden af instruktionsbogen, som indeholder hver VHDL -kodefil, der bruges i projektet.

Indgange

- Clk (native ur signal)

- PP (afspil/pause)

- Sel (sæt synthesizer i valgtilstand)

- Tildel (tildel et trin et trin)

- Trin (positionsnotaterne)

- Freq (switchene skaber den ønskede tonehøjde)

Udgange

- Anode (anoder med 7 segmenter)

- Katode (katoder med 7 segmenter)

- DAC (4-bit driver DAC)

Trin 3: Tekniske detaljer

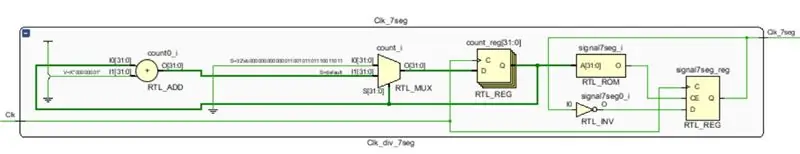

Trin 4: 7-segment Clock Divider

Vores synthesizer gør brug af tre urdelere, der alle producerer signaler, der tjener et andet formål i vores projekt. En urdeler tager et native ur -signal og producerer et ændret signal, som har en frekvens, der er mindre end det originale ur -signal. Det oprindelige ur til Basys 3 er 100 MHz. Dette er den frekvens, vores urdelere bruger. Hvis du bruger et andet FPGA -kort med en anden native clock -frekvens, skal du muligvis ændre koden.

7-segment urdeleren producerer et signal, der driver seg_display-filen. Vi vil forklare, hvordan denne fil fungerer mere detaljeret, når vi kommer til dens sektion. Grundlæggende producerer denne urdeler et 240 Hz signal, der vil blive brugt til at skifte mellem anoder og katoder på displayet. Signalet er 240 Hz, fordi frekvensen, hvormed det menneskelige øje ikke kan genkende fraværet af lys er 60 Hz. Vi bruger to cifre, så ved at fordoble denne frekvens vil hvert ciffer svinge ved 60 Hz. Derefter fordobler vi det for at få 240 Hz, fordi systemet kun ændrer sig, når signalet går højt, ikke når det går lavt.

For at opnå dette tager divideren det native 100 MHz signal og tæller op på hver stigende kant. Når tælleren når 416667, går output fra lavt til højt eller omvendt.

Indgange

Clk (native ur signal)

Udgange

Clk_7seg (til seg_display)

Komponenter

- D registrere

- MUX

- Inverter

- Adder

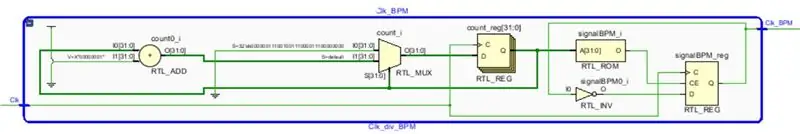

Trin 5: Beats Per Minute Clock Divider

BPM -urdeleren fungerer på en lignende måde. Denne divider producerer den clockfrekvens, der driver skiftet mellem de fire trin, når toner udsendes i afspilningstilstanden. Vi besluttede at skifte mellem noter ved 100 BPM. Ved 100 BPM vil hver note blive spillet i 3/5 sekund. Det resulterende signal ville have en frekvens på 1,67 Hz.

For at producere et signal om denne frekvens brugte vi igen et tællesystem, men denne gang var tællingen 60 millioner. Hver gang tælleren ramte 60 millioner, ville output -signalet skifte højt eller lavt.

Indgange

Clk (native clock frekvens)

Udgange

Clk_BPM (til output_FSM)

Komponenter

- D registrere

- MUX

- Inverter

- Adder

Trin 6: Pitches Clock Divider

Pitches Clock Divider er den største af vores urdelere. Denne divider sender 12 forskellige signaler svarende til de 12 forskellige toner, som vores synthesizer kan afspille. Ved hjælp af grundlæggende viden om musikteori, udledte vi, at en bit eller bus kunne svinge med en hastighed, der svarer til frekvensen af musiknoter. For at se de frekvenser, vi brugte, skal du se her. Vi brugte den fjerde oktav af tonehøjder.

Det samme tællingssystem bruges her. For de specifikke værdier, vi tællede til, se filen mærket Clk_div_pitches.

Indgange

Clk (native clock frekvens)

Udgange

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (til output_select)

Komponenter

- D registrere

- MUX

- Inverter

- Adder

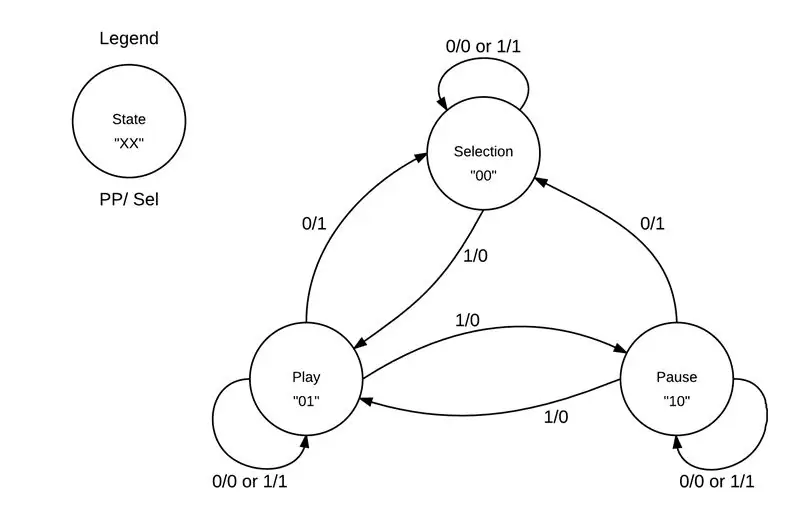

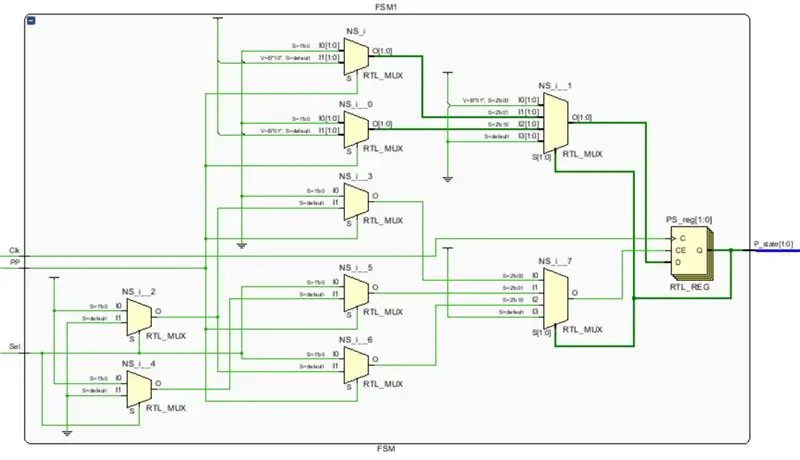

Trin 7: Afspil/Pause/Vælg statsmaskine

I vores projekt er der to finite state machines (FSM). En FSM er en logisk enhed, der kun kan eksistere i en tilstand ud af en begrænset mængde stater. Ved hjælp af en FSM kan et digitalt kredsløb flytte til en ny tilstand baseret på en kombination af input. Ved hjælp af inputlogik ændres en FSM -tilstand, når der er en stigende kant på uret. Fra tilstanden og input til kredsløbet kan du oprette outputlogik, der giver output, der kun eksisterer, hvis FSM er i en bestemt tilstand.

PPS -tilstandsmaskinen er den første FSM i vores kredsløb. Der er tre stater i denne FSM; Afspilning, pause og valgtilstand. For at bevæge os gennem de forskellige tilstande brugte vi knapperne PP og Selection. Se tilstandsdiagrammet ovenfor for at se, hvordan overgange mellem tilstande opstår. Vi foretog denne FSM -overgang på den stigende kant af det oprindelige 100 MHz -ur, så det ville være umuligt for maskinen ikke at skifte, når der blev trykket på en af knapperne, selv i meget kort tid. Den nuværende tilstand (P_state) er den eneste output fra dette modul.

Indgange

- Clk (native clock frekvens)

- Sel (venstre knap)

- PP (højre knap)

Udgange

P_state (nuværende tilstand, til output_FSM, note_assign, seg_dsiplay, final_select)

Komponenter

- MUX

- D registrere

Trin 8: Afspil/Pause/Vælg tilstandsmaskine

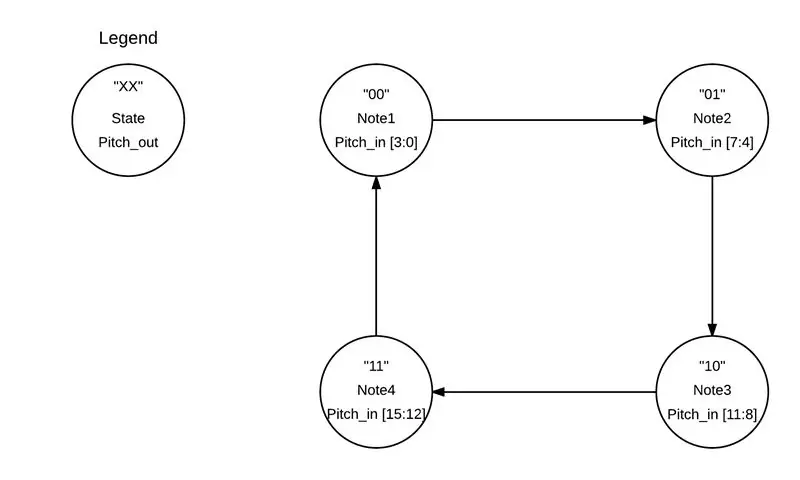

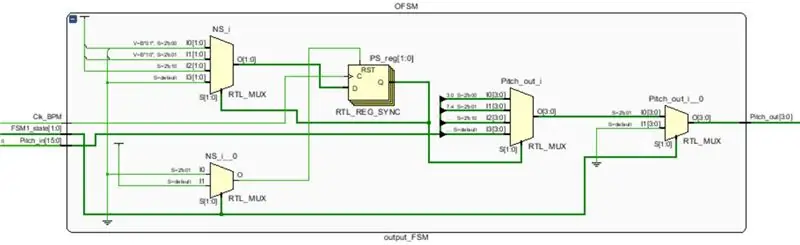

Trin 9: Output FSM

Dette er den anden FSM, der refereres til i det foregående afsnit. Denne FSM tjener en anden funktion end den anden, men grundlaget for denne er i det væsentlige det samme.

Output FSM fungerer kun, hvis den nuværende tilstand fra den første FSM er "01" (afspilningstilstanden). I det væsentlige er dette mulighed for modulet. Hvis tilstanden er "01", vil FSM skifte mellem tilstande på den stigende kant af BPM -kloksignalet. Vi gør dette, fordi output_FSM styrer, hvilket binært tal for den valgte pitch bliver sendt til output_select og seg_display modulerne. FSM har en 16-bit input, der kommer fra note assign-modulet, som derefter vil blive dækket. I tilstanden "00" for output_FSM udsender modulet "xxxx" for den første tildelte note. Så i "01" udsender den "åååå" for den anden note og så videre for hver note, før den ruller tilbage til den første note. Se tilstandsdiagrammet ovenfor.

Denne FSM adskiller sig fra den første, fordi der ikke er nogen inputlogik til at styre skift mellem stater. I stedet vil FSM kun fungere, når tilstanden fra den første FSM er "01", og derefter vil denne FSM kun overgå mellem stater på den stigende kant af urets signal. En anden forskel er, at dette modul har outputlogik, hvilket betyder, at det ikke udsender den nuværende tilstand, det udsender det binære tal for tonehøjden ved denne tilstand.

Indgange

- Clk_BPM (BPM ur signal fra ur divider)

- FSM1_state (PS fra PPS FSM)

- Pitch_in (pladser fra note_assign)

Udgange

Pitch_out (en pitch ad gangen, for output_select og seg_display)

Komponenter

- MUX

- D registrere

Trin 10: Output FSM

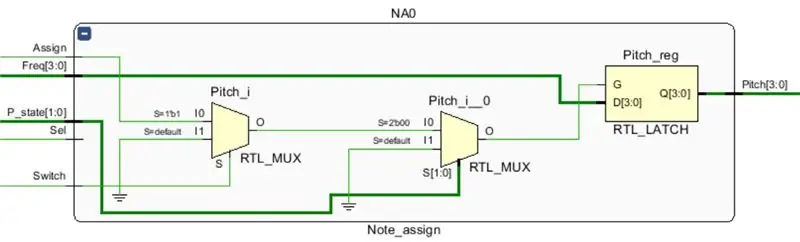

Trin 11: Bemærk Tildel

Note -tildelingsmodulet er ansvarligt for faktisk at tildele en pitch til positionsnoten eller -trinnet. Dette modul er faktisk ganske enkelt. Den kontrollerer først, om kredsløbet er i "valg" -tilstand, og om en trinkontakt (yderst til venstre) er høj. Hvis dette er sandt, og der trykkes på tildelingsknappen, vil modulets output være lig med det binære tal repræsenteret af frekvensomskifterne (helt til højre).

Oprindeligt havde vi forsøgt at lave et modul, der rent faktisk ville gemme et af pitchurssignalerne til output, men vi oplevede problemer med output, der ændrede sig for at følge input -clock -signalerne. Dette er det eneste modul, der bruges mere end én gang i det endelige design. Hvert trin har et note_assign -modul tilknyttet, og på grund af det får hver instans af modulet en bit af Step -bussen.

Indgange

- P_state (nuværende tilstand fra PPS FSM)

- Sel (venstre knap)

- Kontakt (et -trins switch)

- Freq (yderste højre switch til pitch)

- Tildel (nederste knap, tildel en note)

Udgange

Pitch (binært tal, til output_FSM)

Komponenter

- MUX

- D resgister

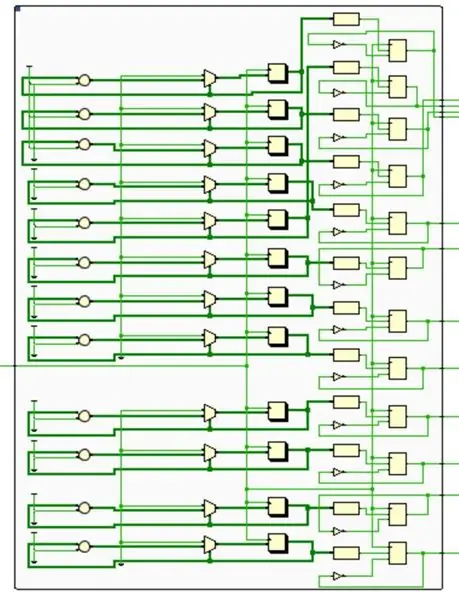

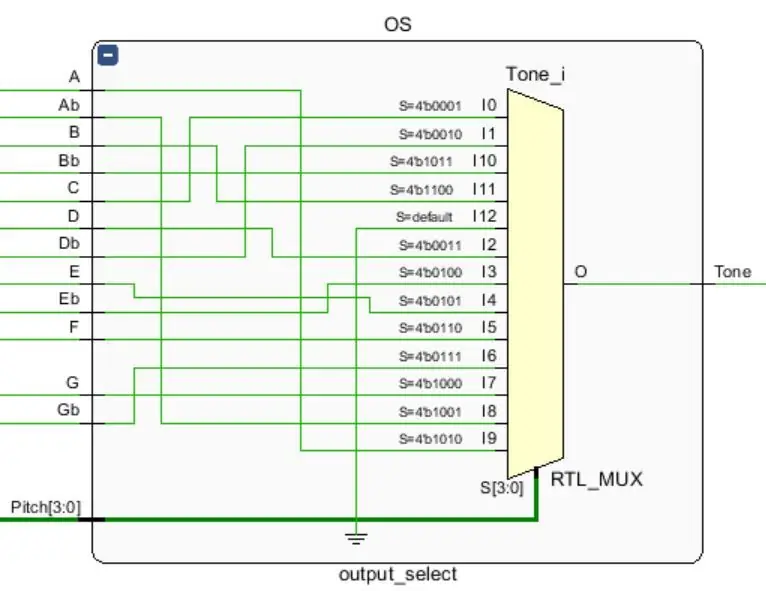

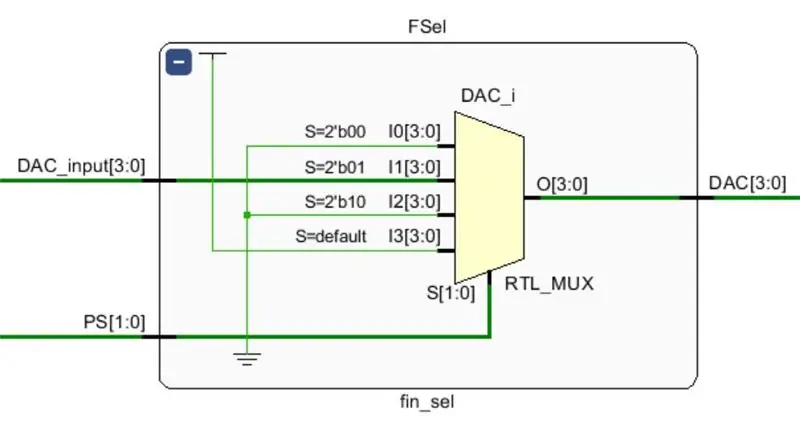

Trin 12: Vælg output

Output select er ansvarlig for at tage det binære tal for en tonehøjde og tilslutte det til dets respektive kloksignal. På trods af sin størrelse er dette også et relativt simpelt modul. Output_select er i det væsentlige en binær dekoder, der afkoder det binære tal for en tonehøjde til et specifikt kloksignal. Faktisk fungerede tildeling af output til en urfrekvens bedre her sammenlignet med note_assign -modulet, fordi alt dette modul skulle gøre var MUX urets signaler med det binære tal, der repræsenterer kontrolindgangen.

Vi beklager den mærkelige routing, Vivado organiserede tonehøjdesignalerne alfabetisk for filen clk_div_pitches, men for denne fil organiserede de dem ved at stige binært tal, hvilket fik tonehøjderne til at være i en anden rækkefølge. Bemærk også, at hvis det binære tal fra output_FSM var "0000" eller noget større end "1100", sendte MUX'en et fladt '0' -signal.

Input

- Pitch (fra output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (toneurssignaler)

Produktion

Tone (en enkelt bit, der matcher det valgte kloksignal, til square_wave)

Komponenter

MUX

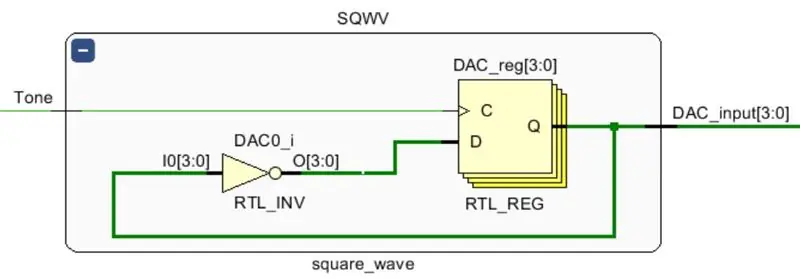

Trin 13: Square Wave Gen

Modul square_wave er generatoren for firkantbølgen, der udsendes fra kortet til DAC. Ved hjælp af tonesignalet fra den forrige fil inverterer denne square_wave 4 bit -tallet mellem "0000" og "1111" på den stigende kant af Tone. Tone er en bestemt tonehøjdefrekvens, så square_wave producerer en bølge med en anden frekvens, når output_FSM overgår til en anden tilstand. 4-bit output fra dette modul går til fin_sel modulet, hvor logik dikterer om denne bus vil blive udsendt baseret på tilstanden fra PPS FSM.

Et alternativ til denne firkantbølge generator genererer en sinusbølge. Selvom dette sandsynligvis ville give en bedre slut tone, er det betydeligt vanskeligere at implementere, så vi valgte bare at generere en firkantbølge.

Indgange

Tone (oscillerende bit fra output_select)

Udgange

DAC_input (oscillerende 4-bit bus, der ændres ved samme tonefrekvens)

Komponenter

- Inverter

- D registrere

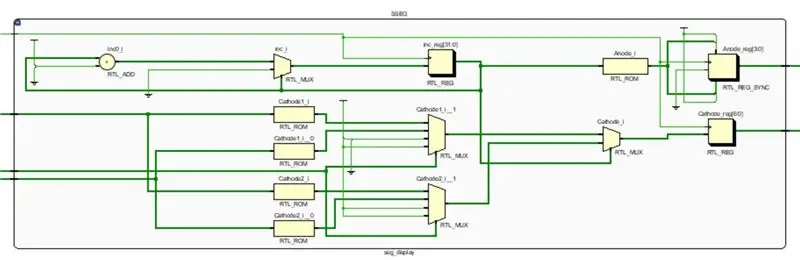

Trin 14: 7-segment display

Seg_display modulet styrer 7-segment displayet på vores basys board. Inden for modulet sker der to processer. Den første proces afkoder Freq, når den er i "valg" -tilstand eller Pitch, når den er i "play" -tilstand. I tilstanden "pause" afkoder modulet for at vise pausesymbolet. Når man ser på VHDL -koden, kan man se, at den binære dekoder faktisk afkoder input til to forskellige signaler, cathode1 og cathode2. Katode1 repræsenterer det bogstav, der svarer til den tonehøjde, der skal vises, og katode2 repræsenterer det flade symbol (b), hvis der er et. Årsagen hertil vedrører den anden proces udført af seg_display -modulet.

På et basys3 -bord har segmentdisplayet fælles katoder. Mens anoderne styrer, hvilket ciffer der er tændt, kontrollerer katoderne, hvilke segmenter der er tændt. Da displayet har fælles katoder, betyder det, at du kun kan vise et sæt segmenter ad gangen. Det udgør et problem for dette projekt, fordi vi vil vise et bogstav med det første ciffer og det flade symbol, om nødvendigt samtidig. Kan du nu huske 7seg urets signal? For at komme uden om dette problem ændrer vi anoder og katoder frem og tilbage på 7seg urets signal. Fordi urets signal er 240 Hz, og vi bruger to cifre, vil hvert ciffer svinge ved 60 Hz. For det menneskelige øje vil det se ud som om cifrene slet ikke svinger.

Bemærk også, at basys3 board -displayet anvender negativ logik. Dette betyder, at hvis en anode eller katode er indstillet til '0', vil dette ciffer eller segment være tændt og omvendt.

Indgange

- Pitch (binært tal for en note, brugt i afspilningstilstand)

- Freq (frekvensomskiftere, bruges i valgtilstand)

- P_state (nuværende tilstand fra PPS FSM)

- Clk_240Hz (ur signal fra Clk_div_7seg, dobbelt 120 fordi vi kun bruger den stigende kant)

Udgange

- Katode (bus, der styrer segmenter på displayet, endelig output)

- Anode (bus, der styrer cifre på displayet, slutudgang)

Komponenter

- Lås

- MUX

- D registrere

Trin 15: Endeligt valg

Endeligt valg er det sidste modul, der blev brugt i dette projekt. Et andet simpelt modul, dette modul styrer det endelige output, der skal til DAC. I tilstanden "valg" eller "pause" sender modulet et statisk "0000", så der ikke afspilles musik fra højttalerne. I tilstanden "play" udsender modulet de oscillerende 4-bit som bestemt af square_wave.

Indgange

- P_state (nuværende tilstand fra PPS FSM)

- DAC_input (de oscillerende 4-bit fra square_wave)

Udgange

DAC (svarer til DAC_input i afspilningstilstand, sidste output)

Komponenter

MUX

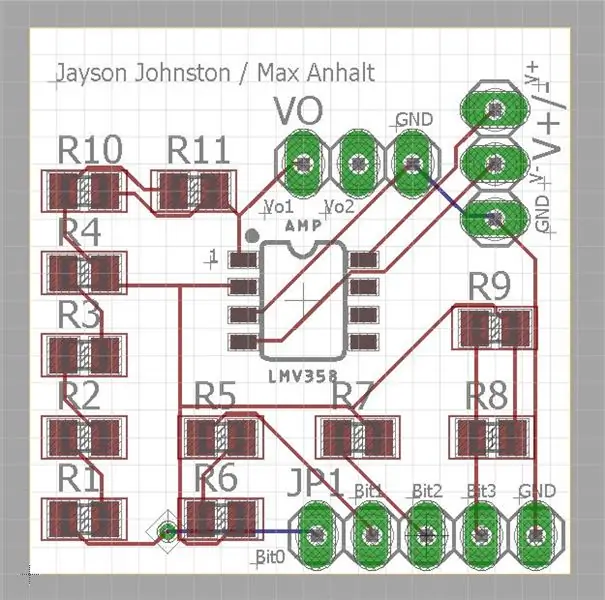

Trin 16: Eksterne enheder: DAC

En digital til analog omformer (DAC) tager et diskret signal og konverterer det til et kontinuerligt signal. Vores DAC har fire bits og er lavet af en summerende forstærker. Ved at bruge et forhold mellem modstande i forsynings- og tilbagekoblingssløjfen var vi i stand til at oprette et system, der udsender på 16 forskellige niveauer, der skabes ved "summering" af hver gren. Bit0, den øverste gren, bærer mindst vægt og bidrager med det mindste potentiale, når den er høj på grund af den forgrener højere modstand. Vægten stiger, når du går ned af grenene. Hvis du skulle tælle i binær op og derefter ned igen ved hjælp af bitindgangene, ville udgangsspændingerne ligne en trinvis sinusbølge. Input til DAC blev forbundet til en af PMOD'erne på kortet for at overføre 4-bit signalet.

DAC'en blev oprindeligt samlet til en elektroteknisk klasse og blev designet og loddet af os, ikke købt fra en butik. Ovenstående er et billede af designfilen til oprettelse af printkortet.

Trin 17: Eksterne enheder: Højttaler

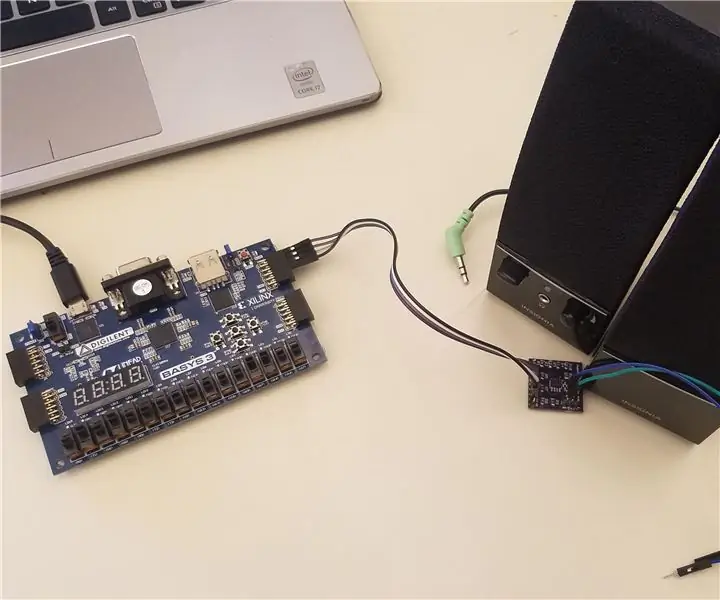

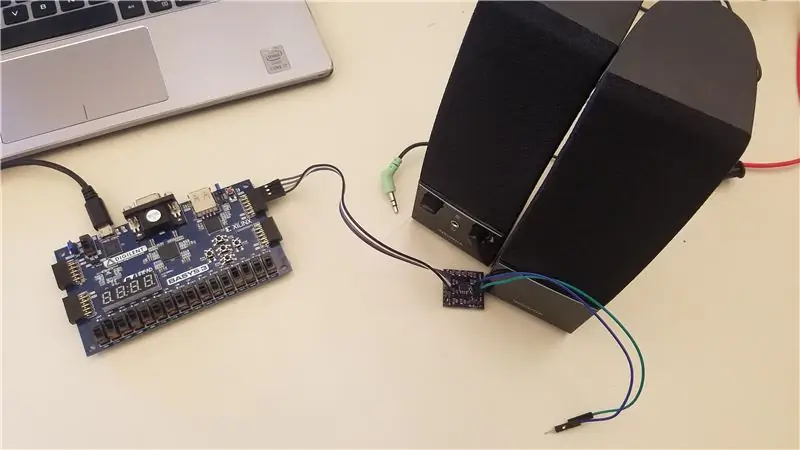

Til dette projekt har du ikke lyst til at købe et super flot par højttalere. Som du kan se, er lyden temmelig grundlæggende. Vi gik og købte et sæt computerhøjttalere på $ 8 fra Best Buy. Alt med hovedtelefonstik fungerer fint. Monoton fungerer også fint. Du kan endda bruge hovedtelefoner, men du kan blæse dem ud!

For at forbinde udgangen fra DAC til højttalerne brugte vi jumperkabler og holdt derefter udgangskablet til spidsen af hovedtelefonstikket og kablet til jord til basen. Vi forsøgte at bruge elektrisk tape til at holde kablerne på plads, men det forårsagede meget interferens. At prøve en anden båndstil kan løse dette problem.

For vores højttalere vendte vi dem til den højeste indstilling og fik en anstændig høj lyd.

Og det er det sidste trin for at oprette en digital sequencer fra et FPGA -kort! Gå til de næste to sektioner for at downloade alle vores VHDL -koder og se sequencer i aktion.

Trin 18: Videodemo

Denne video viser den endelige version af arbejdsprojektet, herunder processen med at tildele switcherne til 4 forskellige pitches, og højttalerne spiller de respektive noter.

Trin 19: VHDL -kode

Her er koden for hele projektet, inklusive begrænsningen og sim -filer, der blev brugt, mens du bygger sequencer. Bemærk, at ubrugte designfiler siger det i arkitekturen.

Anbefalede:

Sådan gør du: Installation af Raspberry PI 4 Headless (VNC) med Rpi-imager og billeder: 7 trin (med billeder)

Sådan gør du: Installation af Raspberry PI 4 Headless (VNC) med Rpi-imager og billeder: Jeg planlægger at bruge denne Rapsberry PI i en masse sjove projekter tilbage i min blog. Tjek det gerne ud. Jeg ville tilbage til at bruge min Raspberry PI, men jeg havde ikke et tastatur eller en mus på min nye placering. Det var et stykke tid siden jeg konfigurerede en hindbær

Sådan adskilles en computer med nemme trin og billeder: 13 trin (med billeder)

Sådan adskilles en computer med nemme trin og billeder: Dette er en instruktion om, hvordan du adskiller en pc. De fleste af de grundlæggende komponenter er modulopbyggede og nemme at fjerne. Det er dog vigtigt, at du er organiseret omkring det. Dette hjælper med at forhindre dig i at miste dele og også ved at lave genmonteringen til

Sådan styrer du husholdningsapparater med fjernsyn med fjernbetjening med timerfunktion: 7 trin (med billeder)

Sådan styrer du husholdningsapparater med fjernsyn med fjernbetjening med timerfunktion: Selv efter 25 års introduktion til forbrugermarkedet er infrarød kommunikation stadig meget relevant i de seneste dage. Uanset om det er dit 55 tommer 4K -fjernsyn eller dit billydsystem, har alt brug for en IR -fjernbetjening for at reagere på vores

Iron Man Reactor for Fun (Digital joystick til digital bevægelse): 7 trin (med billeder)

Iron Man Reactor for Fun (Digital Motion Processor Joystick): Hej kære! Dette er min første instruktion, så håber på din fordel og feedback! Projektet er en interaktiv platform til hjemmefester, konkurrencer, events - bare for sjov. Disse er to bevægelsessensorer fremstillet i designet af jernmandsreaktoren. Det

Genbrugt digital fotoramme med virtuel assisterende: 7 trin (med billeder)

Genbrugt digital fotoramme med virtuel assisterende: Hej alle sammen! Denne instruktør blev født fra en bærbar computer delt i to, købt af en ven. Det første forsøg på et sådant projekt var min Lego Digital fotoramme, men da jeg var en entusiastisk bruger af Siri og Google Now, besluttede jeg at tage det til en ny