Indholdsfortegnelse:

- Trin 1: Byg elektronisk kredsløb

- Trin 2: Kontroller Pin Planner, og rediger Verilog -kode

- Trin 3: Rediger Verilog -kode

- Trin 4: Kompiler Verilog -kode

- Trin 5: Lad os prøve det

Video: FPGA Cyclone IV DueProLogic - Trykknap og LED: 5 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:25

I denne vejledning vil vi bruge FPGA til at styre eksternt LED -kredsløb. Vi skal gennemføre følgende opgaver

(A) Brug trykknapperne på FPGA Cyclone IV DuePrologic til at styre LED.

(B) Flash LED tændes og slukkes med jævne mellemrum

Video demo

Lab-menu: https://roywchpi.blogspot.com 2020/06/10-fpga-dueprologic-push-button-led.html

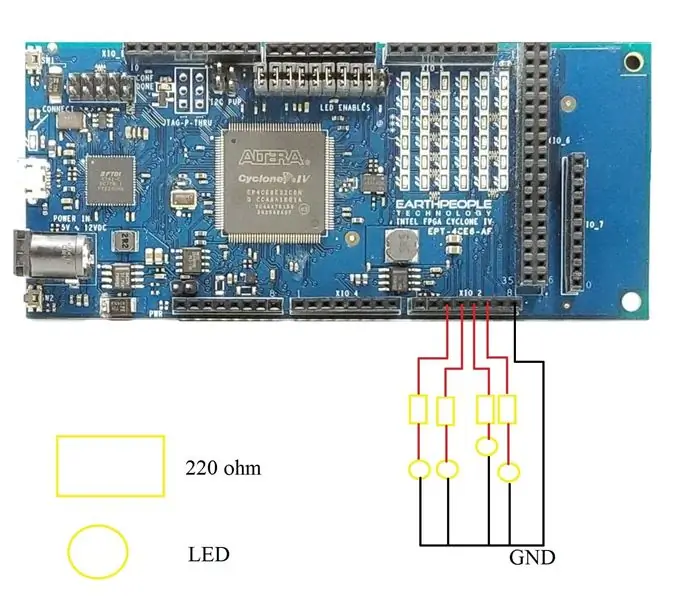

Trin 1: Byg elektronisk kredsløb

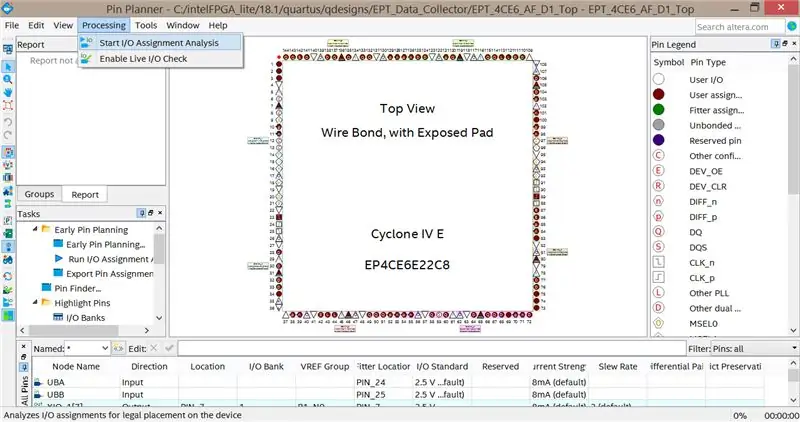

Trin 2: Kontroller Pin Planner, og rediger Verilog -kode

Trin 3: Rediger Verilog -kode

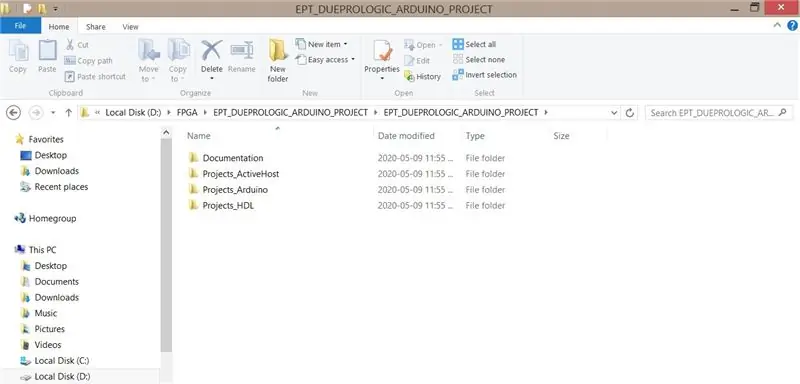

Når du køber FPGA DueProLogic, skal du modtage en dvd. Når du har åbnet "Projects_HDL", skal du se den originale kodefil

Tilføj den markerede kode. Det registrerer I/O -portene og tildeler numre til portene.

outputledning [7: 0] XIO_1, // XIO-D2-D9

udgangskabel [5: 0] XIO_2, // XIO-D10-D12

udgangskablet [5: 0] XIO_3, // XIO-D22-D29

inputledning [5: 0] XIO_4, // XIO-D30-D37

inputledning [5: 0] XIO_5, // XIO-D38-D45

udgangskablet [4: 0] XIO_6_OUT, // XIO-D46-D53

inputledning [31: 5] XIO_6, // XIO-D46-D53

udgangskabel [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

input wire UBA, // Push Button Switches

input wire UBB // Trykknapkontakter

tildele XIO_1 [3] = start_stop_cntrl;

tildele XIO_2 [1] = start_blinky; // LED flash LED tændt og slukket

tildele XIO_2 [2] = 1'b1; // output HIGH

tildele XIO_2 [3] = ~ UBA; // Trykknap A

tildele XIO_2 [4] = UBB; // Tryk på knap B

tildele c_enable = XIO_5 [2];

tildele LEDExt = XIO_5 [5];

Derefter skal vi indstille en forsinkelsestimer. Kommenter den originale timerkode, og skriv en ny timerfunktion

//-----------------------------------------------

// LED Blinkende start

//-----------------------------------------------

/*

altid @(posedge CLK_66 eller negedge RST)

begynde

hvis (! RST)

start_blinky <= 1'b0;

andet

begynde

hvis (control_register [7: 4]> 0)

start_blinky <= 1'b1;

andet

start_blinky <= 1'b0;

ende

ende

*/

reg [31: 0] eks;

første begyndelse

eks <= 32'b0;

start_blinky <= 1'b0;

ende

altid @(posedge CLK_66)

begynde

ex <= ex + 1'b1;

hvis (ex> 100000000) // flash tænd/sluk ~ 1,6 sekunder, ur 66MHz

begynde

start_blinky <=! start_blinky;

eks <= 32'b0;

ende

ende

//-----------------------------------------------

// LED Delay Timer Counter

//-----------------------------------------------

/*

altid @(posedge CLK_66 eller negedge RST)

begynde

hvis (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

andet

begynde

hvis (angiv [SELECT_MODE])

led_delay_counter <= timer_value;

ellers hvis (angiv [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

ende

ende*/

Trin 4: Kompiler Verilog -kode

Tryk på "Start kompilering" i Quartus, der bør ikke genereres en fejlmeddelelse.

Hvis du modtager en fejlmeddelelse om flere pins. Gå til Opgaver -> Enhed -> Enheds- og pinindstillinger -> Dual -Purpose Pins -> ændre værdien af den relevante pin til "Brug som almindelig I/O".

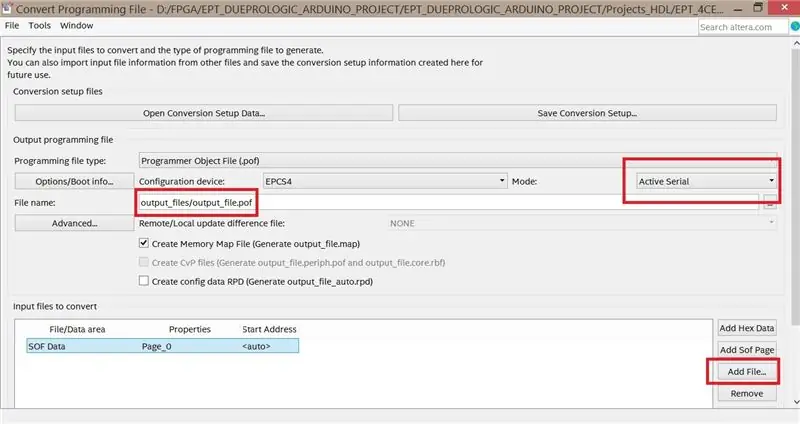

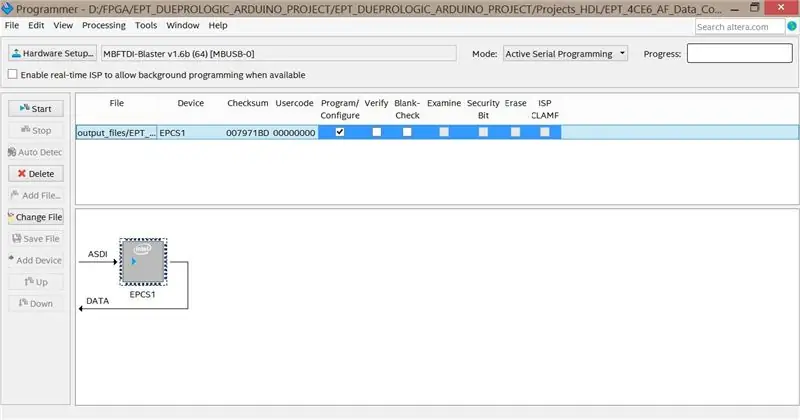

Efter kompilering skal du få pof -outputfil direkte. Hvis din software ikke er opdateret, får du muligvis kun sof-fil. Når det sker, skal du klikke på "File" i Quartus -> "konverter programmeringsfiler". Skift de indstillinger, der er markeret med røde felter.

Trin 5: Lad os prøve det

Det skulle jo fungere !!! Den gule LED er altid tændt. Den røde LED blinker. Den blå lysdiode slukkes, hvis du trykker på knap B. Den grønne lysdiode tændes, hvis du trykker på knap A

Anbefalede:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: 5 trin

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: På trods af at FPGA DueProLogic er officielt designet til Arduino, vil vi gøre FPGA og Raspberry Pi 4B overførbare. Tre opgaver implementeres i denne vejledning: (A) Tryk samtidigt på de to trykknapper på FPGA for at vende vinklen på

FPGA Cyclone IV DueProLogic Controls Servomotor: 4 trin

FPGA Cyclone IV DueProLogic Controls Servomotor: I denne vejledning skal vi skrive Verilog -kode til styring af servomotor. Servoen SG-90 er fremstillet af Waveshare. Når du køber servomotoren, modtager du muligvis et datablad, der viser driftsspændingen, det maksimale drejningsmoment og det foreslåede Pu

DIY VR løbebånd- Basys3 FPGA-Digilent konkurrence: 3 trin

DIY VR løbebånd- Basys3 FPGA-Digilent konkurrence: Vil du bygge en VR løbebånd, hvor du kan køre dine desktop applikationer og spil? Så er du kommet til det rigtige sted! I konventionelle spil bruger du musen og tastaturet til at interagere med miljøet. Derfor skal vi sende

Arduino Cyclone Game: 5 trin (med billeder)

Arduino Cyclone Game: Jeg har aldrig spillet det rigtige cyklonarkadespil, men jeg kan godt lide tanken om at spille med vores reaktionstid. Jeg designede et miniaturiseret spil. Den består af 32 lysdioder, der danner en cirkel, lysdioderne lyser en efter en som en led chaser. Målet er at trykke på en knap

Arduino Cyclone Arcade Game: 6 trin

Arduino Cyclone Arcade Game: Blinkende prangende lys! Arduino! Spil! Hvad mere skal der siges? Dette spil er baseret på Cyclone -arkadespillet, hvor spilleren forsøger at stoppe en led, der ruller rundt i en cirkel på et bestemt sted