Indholdsfortegnelse:

- Trin 1: Hent hardware/software

- Trin 2: Blokdiagram

- Trin 3: Projektmodul

- Trin 4: Begrænsninger

- Trin 5: Test

Video: VHDL Et minuts stopur: 5 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:29

Dette er en vejledning i, hvordan du opbygger et stopur på et minut ved hjælp af VHDL og et Basys 3 -kort. Sådan en enhed er ideel til spil, hvor hver spiller maksimalt har et minut til at foretage sit træk. Stopuret viser nøjagtigt sekunder og millisekunder på displayet med syv segmenter, der starter med 0 sekunder og 0 millisekunder, op til 60 sekunder og 0 millisekunder. To knapper bruges også: den centrale knap, der bruges til at starte, stoppe og fortsætte timeren, og den højre knap, bruges til at genstarte timeren. Når enheden sammenlignes side om side med det indbyggede stopur på en smartphone, er urets nøjagtighed mærkbar.

Trin 1: Hent hardware/software

1. Basys 3 Artix-7 FPGA Trainer Board fra Digilent med Micro-USB til USB-kabel

2. Vivado 2016.2 Design Suite fra Xilinx

Trin 2: Blokdiagram

Dette kredsløb er konstrueret adfærdsmæssigt og bruger indbyggede Xilinx-komponenter, men kan også beskrives strukturelt, som vist af det generelle strukturdiagram ovenfor. Af diagrammet kan det ses, at kredsløbet drives af to frekvensdelere. En af frekvensdelerne kører på 1 centisekund og driver katodetælleren, der bruges som de tal, der vises på syv-segment displayet. Den anden frekvensdeler kører ved 240Hz og bruges til at drive anodetælleren, der roterer gennem anoderne, så alle tallene vises korrekt på syvsegmentets display. Koderen tager katodelogikken fra katodetælleren og anodelogikken fra anodetælleren og koder den til outputets katode og anode, der kører det syv-segmenters display. Funktionen af denne encoder er, at katodeudgangen ændres hver gang anodeudgangen ændres. Katodeudgangen kan ikke køres uafhængigt af tælleren, fordi anoderne skal rotere gennem de 4 separate cifre.

Trin 3: Projektmodul

For det første laves en procesblok for CEN, så når en knap Tryk registreres, vil ENABLE skifte. Dette fungerer som stop/start af katodetælleren.

I den næste procesblok indstilles centisekund og 240Hz urssignaler, så deres respektive tællere stiger med 1 hver gang det interne 100mHz ur når en stigende kant. Når centisekundstælleren når 500000, nulstilles den tilbage til 0. I mellemtiden nulstilles 240Hz -tælleren, når tællingen når 41667.

For katodesektionen i koden, hvis ENABLE er '0', stopper katodetællingen. Hvis der trykkes på reset -knappen i løbet af denne tid, nulstilles alle tællingerne til "0000". I mellemtiden, hvis ENABLE er '1', fortsætter katodtællingen, indtil katodeantallet når 60,00, hvor det udløser stopsignalet til at være '1'. Stoppesignalet går tilbage til CEN -procesblokken og får ENABLE til at være '0', mens stopsignalet er '1' og ændres ikke, før der trykkes på reset -knappen.

Endelig er det syv segment display konfigureret ved at have de 4 anoder korrekt forbundet med hver af deres 8 katoder for at vise deres respektive cifre 0-9 samtidigt.

Trin 4: Begrænsninger

Denne begrænsningsfil forbinder de angivne input og output fra VHDL til de nødvendige, fysiske dele af Basys -kortet. Til dette projekt omfatter komponenterne de fire anoder og hver af deres otte katoder til syv segment display, det interne 100 mHz ur, midterknappen og den højre knap.

Trin 5: Test

Når du har udfyldt koden, kan du nu programmere FPGA via USB -kablet. Displayet med syv segmenter skal vise 0,00. Test for at se, om knapperne virker ved at trykke på den midterste knap for at starte timeren, indtil den når 60,00 og stopper; når som helst imellem, kan du trykke på den centrale knap igen for at sætte den på pause. Når den er sat på pause, kan du trykke på den højre knap for at nulstille timeren til 0,00. Hvis alt fungerer korrekt, tillykke, du har lige bygget en et minuts timer!

Anbefalede:

Arduino Leonardo stopur: 3 trin

Arduino Leonardo Stopur: Kredit: https://www.instructables.com/id/Arduino-Stopwatch…Dette stopurdesign stammer fra linket ovenfor, som er et stopur, der tæller fra 1, hvorimod dette tæller ned fra 60 sekunder . Det meste af den kode, jeg har brugt, følger originalen

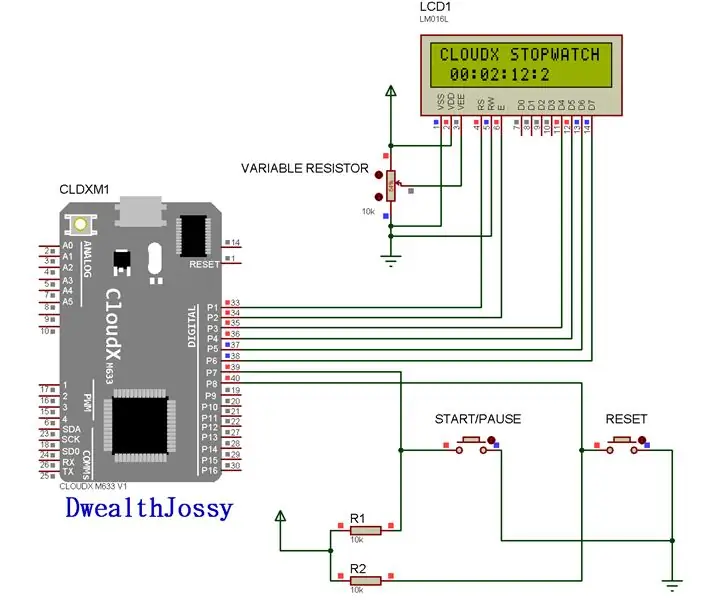

Enkelt CloudX M633 digitalt stopur: 4 trin

Simple CloudX M633 Digital stopur: I dette projekt skal vi lave en version af et digitalt ur, der kan registrere timer, minutter og sekunder, ligesom et stopur på din mobiltelefon! Vi vil bruge en LCD til at vise tiden

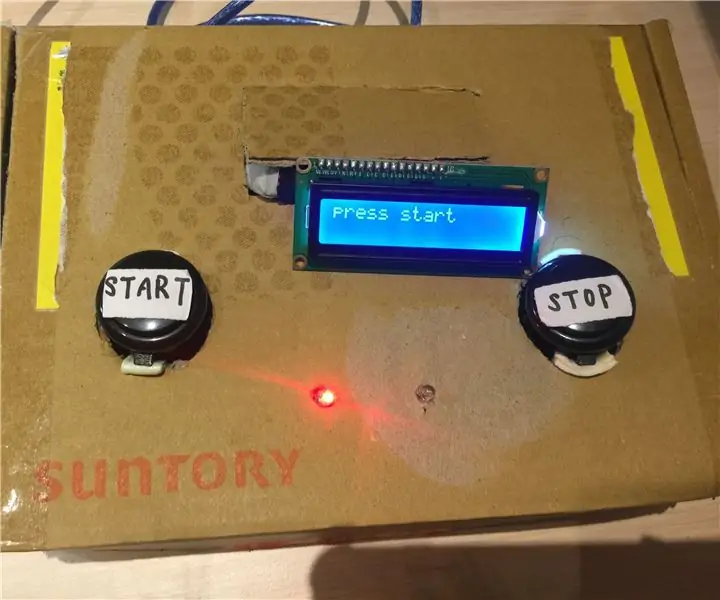

Arduino Project - Stopur: 3 trin

Arduino Project - Stopur: Dette stopur kan bruges til at time alt, hvad du vil, f.eks. Tid, det tager at afslutte en opgave eller give dig selv pres på den tid, der bruges til at afslutte et værk. Lysdioderne hjælper brugeren med tydeligt at kende tidspunktet for start og stop.Dette projekt startede

Grundlæggende stopur ved hjælp af VHDL og Basys3 Board: 9 trin

Grundlæggende stopur ved hjælp af VHDL og Basys3 Board: Velkommen til instruktionsbogen om, hvordan man bygger et stopur ved hjælp af grundlæggende VHDL og Basys 3 board. Vi glæder os til at dele vores projekt med dig! Dette var et afsluttende projekt for kursus CPE 133 (Digital Design) på Cal Poly, SLO i efteråret 2016. Projektet vi byggede

VHDL Stopur: 8 trin (med billeder)

VHDL Stopur: Dette er en vejledning i, hvordan man laver et stopur ved hjælp af VHDL og et FPGA-kredsløb, som et Basys3 Atrix-7-kort. Stopuret kan tælle fra 00,00 sekunder til 99,99 sekunder. Den bruger to knapper, en til start/stop -knappen og en til