Indholdsfortegnelse:

- Trin 1: Hardware/software

- Trin 2: Blokdiagram

- Trin 3: Angiv diagram

- Trin 4: Clock Divider Module

- Trin 5: Displaymodul

- Trin 6: Bindingsmodul

- Trin 7: Begrænsninger

- Trin 8: Udført

Video: VHDL Stopur: 8 trin (med billeder)

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:29

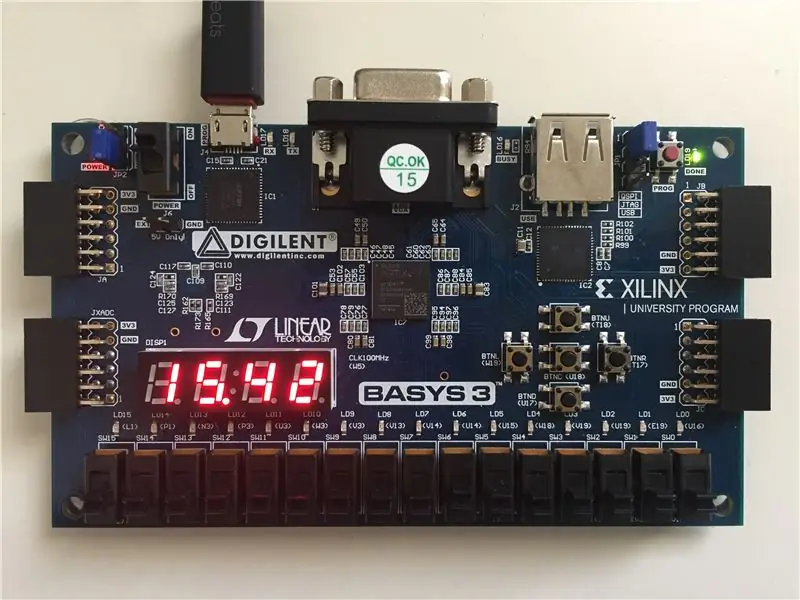

Dette er en vejledning i, hvordan du laver et stopur ved hjælp af VHDL og et FPGA-kredsløb, som et Basys3 Atrix-7-kort. Stopuret kan tælle fra 00,00 sekunder til 99,99 sekunder. Den bruger to knapper, en til start/stop -knappen og en anden til reset -knappen. Tallene vises på tavlens syv-segment display ved hjælp af dets anoder og katoder. Der er tre forskellige filer nødvendige for at få dette stopur til at fungere.

Trin 1: Hardware/software

- Basys3 Atrix-7 FPGA Board

- Vivado Design Suite fra Xilinx

- USB 2.0 A Han til Micro-B Hann

Trin 2: Blokdiagram

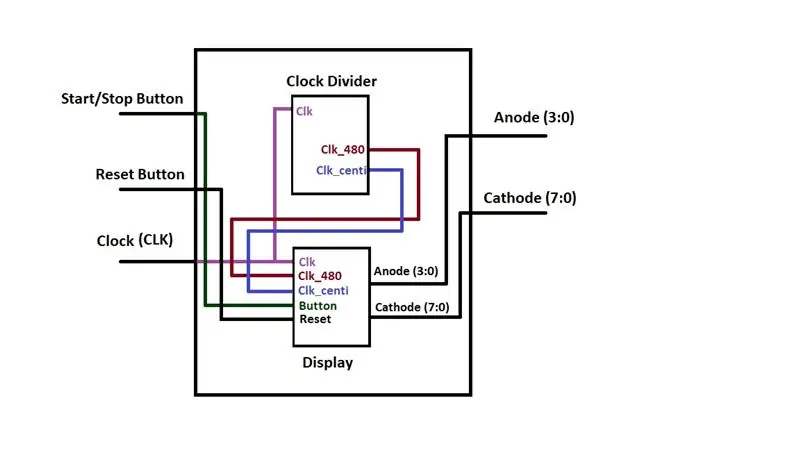

Det samlede stopur har tre indgange og to udgange. De tre indgange er start/stop, nulstilling og ur. Start/stop og nulstilling er knapper, og uret er tavlens 100MHz ur. De to udgange er anoder og katoder til syv-segment displayet.

Det første modul (urdeler) har en indgang og to udgange. Input er kortets 100MHz ur, og udgangene er to separate ure, et kører ved 480Hz og et andet kører 0,5MHz.

Det andet modul (display) har fem indgange og to udgange. Indgangene er tavlens 100MHz ur, de to ure fra urdelermodulet, og start/stop og nulstillingsknapperne. Udgangene er anoder og katoder.

Det sidste modul (modelleret efter hele blokdiagrammet) har tre indgange og to udgange. Dette er filen, der samler alt. Indgangene er tavlens 100MHz og start/stop og nulstillingsknapper. Udgangene er anoder og katoder, der styrer syv-segmentets display. Alle input og output er fysisk på tavlen til det sidste modul.

Trin 3: Angiv diagram

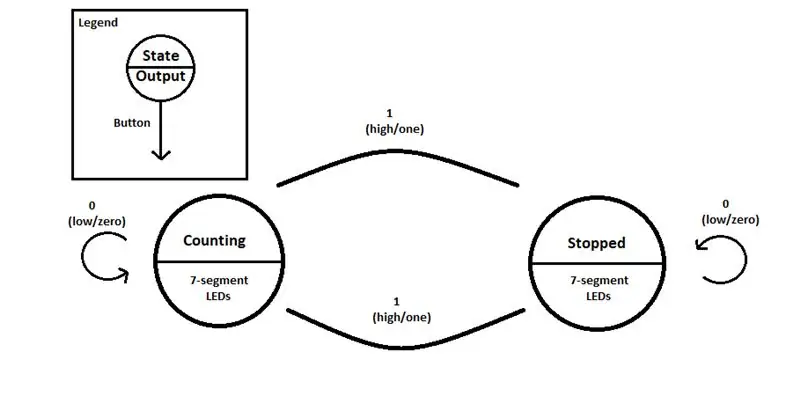

Billedet ovenfor viser tilstandsdiagrammet for, hvordan stopuret fungerer. Tryk på reset -knappen har ingen indflydelse på stopurets tilstand. Den næste tilstand bestemmes af start/stop -knappen. Start/stop er "HØJ", når den trykkes ned, men ikke når den holdes nede, og "LAV", når knappen er slået tilbage eller holdes nede efter at være "HØJ" et øjeblik.

Hvis stopuret tæller, og start/stop -knappen går "HØJ", stopper det med at tælle. Hvis stopuret stoppes, og start/stop -knappen går "HIGH", begynder det at tælle igen. For begge tilstande, hvis start/stop -knappen er "LAV", forbliver den i den tilstand, den er i øjeblikket.

Trin 4: Clock Divider Module

Urdelermodulet har en indgang, kortets 100MHz -ur og to udgange, 480Hz og 0.5MHz -urene. 480Hz-uret bruges til at holde alle lysdioderne på syvsegmentets display "tændt" på samme tid ved hurtigt at skifte gennem de fire. 0.5MHz-uret bruges til stopuret til faktisk at tælle med centi-sekunder.

Trin 5: Displaymodul

Dette displaymodul har fem indgange, tavlens 100MHz ur, de to ure fra urmodulet, start/stop og nulstillingsknapperne og to udgange, anoderne og katoderne. Dette modul har også "logikken" for, hvordan stopuret tæller og inkorporerer den endelige tilstandsmaskine.

Trin 6: Bindingsmodul

Dette sidste modul er det, der samler de to andre moduler. Det har tre indgange, brættets 100MHz ur og start/stop og nulstillingsknapperne og to udgange, anoderne og katoderne. 100MHz -uret går til urdelermodulet og displaymodulet, og start/stop og nulstillingsknapperne går til displaymodulet. Udgangene fra urdelermodulet (480Hz og 0,5MHz) går til de to urindgange på displaymodulet. Udgangene fra displaymodulet (anoder og katoder) går til det sidste moduls output.

Trin 7: Begrænsninger

De to indgange kan være en hvilken som helst knap på Basys3 Atrix-7 FPGA-kortet, og udgangene bliver de fire anoder og de otte katoder (fordi du også vil have et decimalpunkt mellem sekunder og millisekunder) for syv-segment displayet.

Trin 8: Udført

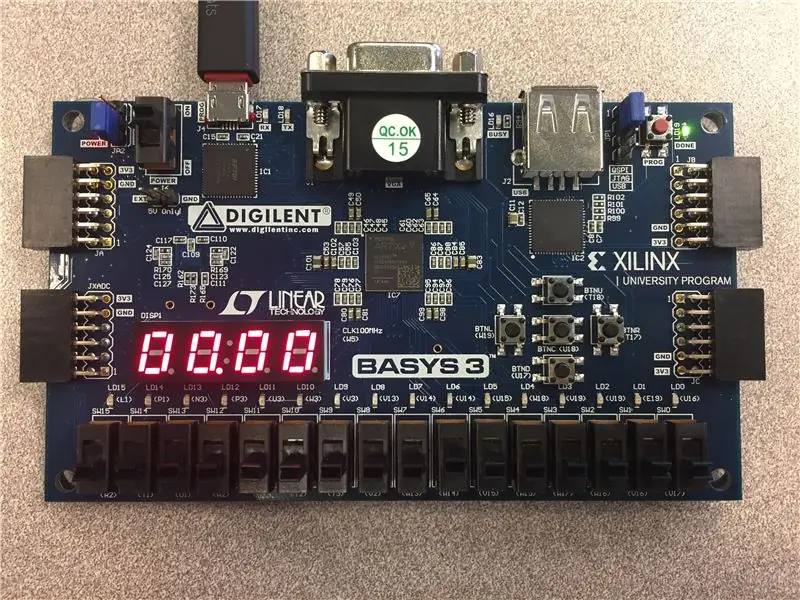

Upload programmet til dit Basys3 Atrix-7 FPGA Board, og tryk på start/stop-knappen for at få stopuret i gang!

Anbefalede:

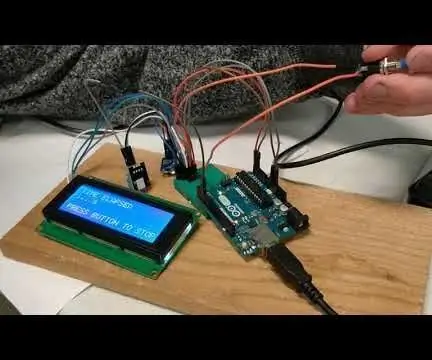

Sådan laver du et stopur ved hjælp af Arduino: 8 trin (med billeder)

Sådan laver du et stopur ved hjælp af Arduino: Dette er et meget simpelt Arduino 16*2 lcd display stopur ……….. Hvis du kan lide denne instruerbare, kan du abonnere på min kanal https://www.youtube.com /ZenoModiff

Grundlæggende stopur ved hjælp af VHDL og Basys3 Board: 9 trin

Grundlæggende stopur ved hjælp af VHDL og Basys3 Board: Velkommen til instruktionsbogen om, hvordan man bygger et stopur ved hjælp af grundlæggende VHDL og Basys 3 board. Vi glæder os til at dele vores projekt med dig! Dette var et afsluttende projekt for kursus CPE 133 (Digital Design) på Cal Poly, SLO i efteråret 2016. Projektet vi byggede

Arduino stopur: 4 trin (med billeder)

Arduino stopur: Denne instruktør viser dig, hvordan du laver et stopur af en Arduino

Enkelt Arduino -ur / stopur: 6 trin (med billeder)

Simpelt Arduino -ur / stopur: Dette " instruerbare " vil vise og lære dig, hvordan du laver et simpelt Arduino Uno -ur, der også fungerer som stopur i bare nogle få, enkle trin

VHDL Et minuts stopur: 5 trin

VHDL One Minute Stopwatch: Dette er en vejledning i, hvordan du opbygger et stopur på et minut ved hjælp af VHDL og et Basys 3 -kort. Sådan en enhed er ideel til spil, hvor hver spiller maksimalt har et minut til at foretage sit træk. Stopuret viser nøjagtigt sekunder og millisekunder