Indholdsfortegnelse:

- Trin 1: VHDL og Modelsim

- Trin 2: VHDL -kode til designet og testbænken

- Trin 3: Vedhæftede filer

- Trin 4: Mini -Cordic IP Core - 16 bit

Video: Cordisk algoritme ved hjælp af VHDL: 4 trin

2024 Forfatter: John Day | [email protected]. Sidst ændret: 2024-01-30 08:26

Af AmCoderhttps://www.linkedin.com/in/mituFølg mere af forfatteren:

Om: Mitu Raj - Bare en hobby og elev - Chip Designer - Softwareudvikler - Fysik og matematikentusiast Mere om AmCoder »

## Dette er det mest klikede, populære link i Google til VHDL -implementering af CORDIC ALGORITHM for at generere sinus- og cosinusbølge ## På nuværende tidspunkt findes der mange hardwareeffektive algoritmer, men disse er ikke velkendte på grund af softwaresystemernes dominans over de mange år. CORDIC er en sådan algoritme, der ikke er andet end et sæt skift og tilføjelseslogik, der bruges til at beregne en lang række funktioner, herunder visse trigonometriske, hyperboliske, lineære og logaritmiske funktioner. Dette er algoritmen, der bruges i regnemaskiner osv. Således kan vi ved blot at bruge simple shifters og adders designe en hardware med mindre kompleksitet, men kraften i DSP ved hjælp af cordic algoritme. Derfor kan den designes som bare RTL -design i VHDL eller Verilog uden brug af dedikerede floating point -enheder eller komplekse matematiske IP'er.

Trin 1: VHDL og Modelsim

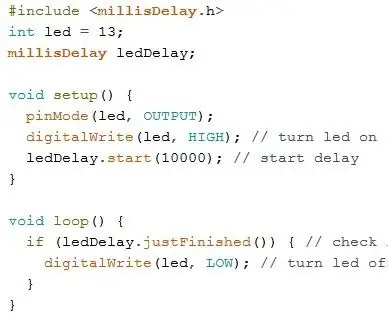

Her implementeres den cordiske algoritme ved hjælp af VHDL til at generere en sinusbølge og cose -bølge. Det kan udsende sinus og cosinus for indgangsvinkel med stor præcision. Koden kan syntetiseres på FPGA. Modelsim bruges til at simulere designet og testbænken.

Trin 2: VHDL -kode til designet og testbænken

Binær skaleringsteknik bruges til at repræsentere flydende tal.

Gå venligst gennem de vedhæftede dokumenter, før du koder.

Gå igennemSimulering af cordic_v4.vhd - Designet -Indgangen er vinkel i 32 bit + tegnbit; den kan behandle enhver vinkel fra 0 til +/- 360 grader med inputpræcision på 0.000000000233 grader. Ved input -> MSB er tegnbit og resten 32 bit repræsenterer størrelse. -Designets output er dens sinus og cos -værdi i 16 bit + tegnbit.ie; med præcision 0.00001526. Bemærk, at output vises i 2's komplimentform, hvis den respektive sinus- eller cos -værdi er negativ. Simulering af testb.vhd - Testbænk til designet (1) Indtastningsvinkler og pull reset = '0'. Efter to trin med simulering træk nulstillingen til '1' og "kør alle". (2) I simuleringsvinduet indstil radixet for sin og cos signaler som decimal og format> Analog (automatisk). (3) Zoom ud for at se kurven korrekt.

Trin 3: Vedhæftede filer

(1) cordic_v4.vhd - Design. (2) testb.vhd - Testbænk til designet.

(3) Dokument om, hvordan man tvinger vinkelindgange og konverterer de binære resultater.

Opdatering: DISSE FILER ER OBSELETE OG LEVERES IKKE MERE. BRUG VENLIGST FILER FRA NÆSTE TRIN

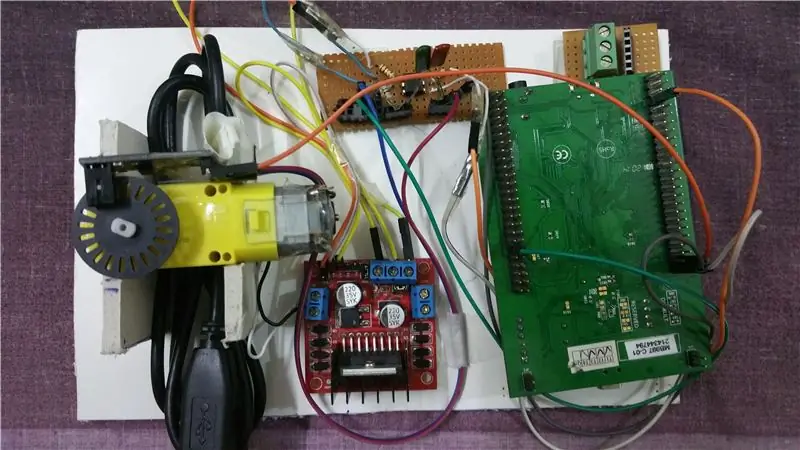

Trin 4: Mini -Cordic IP Core - 16 bit

Begrænsning af ovenstående implementering er- langsom, lavere driftsfrekvens på grund af beregninger i en enkelt urcyklus. Mini-Cordic IP Core- 16 Bit

- Kritiske stier fordelt på flere cyklusser for at forbedre ydeevnen.- Hurtigere- FPGA gennemprøvet design syntetiseret op til 100 Mhz ur.- Mere område optimeret i HDL, mindre hardware.- Load og Done Status signaler tilføjet.- Kun ulempen er mindre opløsning sammenlignet med forrige. Testbench:

fuldstændig automatiseret fra 0 til 360 graders vinkelindgange

Vedhæftede filer: 1) mini cordic main vhdl file2) mini cordic test bench3) Mini Cordic IP Core manual4) Doc om hvordan man tvinger vinkler og konverterer resultater

Hvis du har spørgsmål, er du velkommen til at kontakte mig:

Mitu Raj

følg mig:

mail: [email protected]

### Downloads i alt: 325 fra og med 01-05-2021 ###

### Kode senest redigeret: juli-07-2020 ###

Anbefalede:

DIY -- Sådan laver du en edderkoprobot, der kan kontrolleres ved hjælp af smartphone ved hjælp af Arduino Uno: 6 trin

DIY || Sådan laver du en edderkoprobot, der kan styres ved hjælp af smartphone Brug af Arduino Uno: Mens du laver en edderkoprobot, kan man lære så mange ting om robotik. Ligesom at lave robotter er underholdende såvel som udfordrende. I denne video vil vi vise dig, hvordan du laver en Spider -robot, som vi kan betjene ved hjælp af vores smartphone (Androi

Kontrol ledt over hele verden ved hjælp af internet ved hjælp af Arduino: 4 trin

Kontrol ledt over hele verden ved hjælp af internet ved hjælp af Arduino: Hej, jeg er Rithik. Vi kommer til at lave en internetstyret LED ved hjælp af din telefon. Vi kommer til at bruge software som Arduino IDE og Blynk.Det er enkelt, og hvis det lykkedes dig, kan du styre så mange elektroniske komponenter, du ønskerTing We Need: Hardware:

Sådan laver du en drone ved hjælp af Arduino UNO - Lav en quadcopter ved hjælp af mikrokontroller: 8 trin (med billeder)

Sådan laver du en drone ved hjælp af Arduino UNO | Lav en Quadcopter ved hjælp af mikrokontroller: Introduktion Besøg min Youtube -kanal En Drone er en meget dyr gadget (produkt) at købe. I dette indlæg vil jeg diskutere, hvordan jeg gør det billigt ?? Og hvordan kan du lave din egen sådan til en billig pris … Nå i Indien alle materialer (motorer, ESC'er

Selvbalancerende robot ved hjælp af PID -algoritme (STM MC): 9 trin

Selvbalancerende robot ved hjælp af PID -algoritme (STM MC): For nylig er der blevet arbejdet meget med selvbalancering af objekter. Begrebet selvbalancering startede med balancering af omvendt pendul. Dette koncept omfattede også design af fly. I dette projekt har vi designet en lille mod

Hastighedskontrol af DC -motor ved hjælp af PID -algoritme (STM32F4): 8 trin (med billeder)

Hastighedskontrol af jævnstrømsmotor ved hjælp af PID -algoritme (STM32F4): hej alle sammen, dette er tahir ul haq med et andet projekt. Denne gang er det STM32F407 som MC. Dette er et afslutning på midt semester projekt. Håber du kan lide det. Det kræver mange begreber og teori, så vi går først ind på det. Med fremkomsten af computere og